Chapter 4 INTERFACE SETTINGS

119

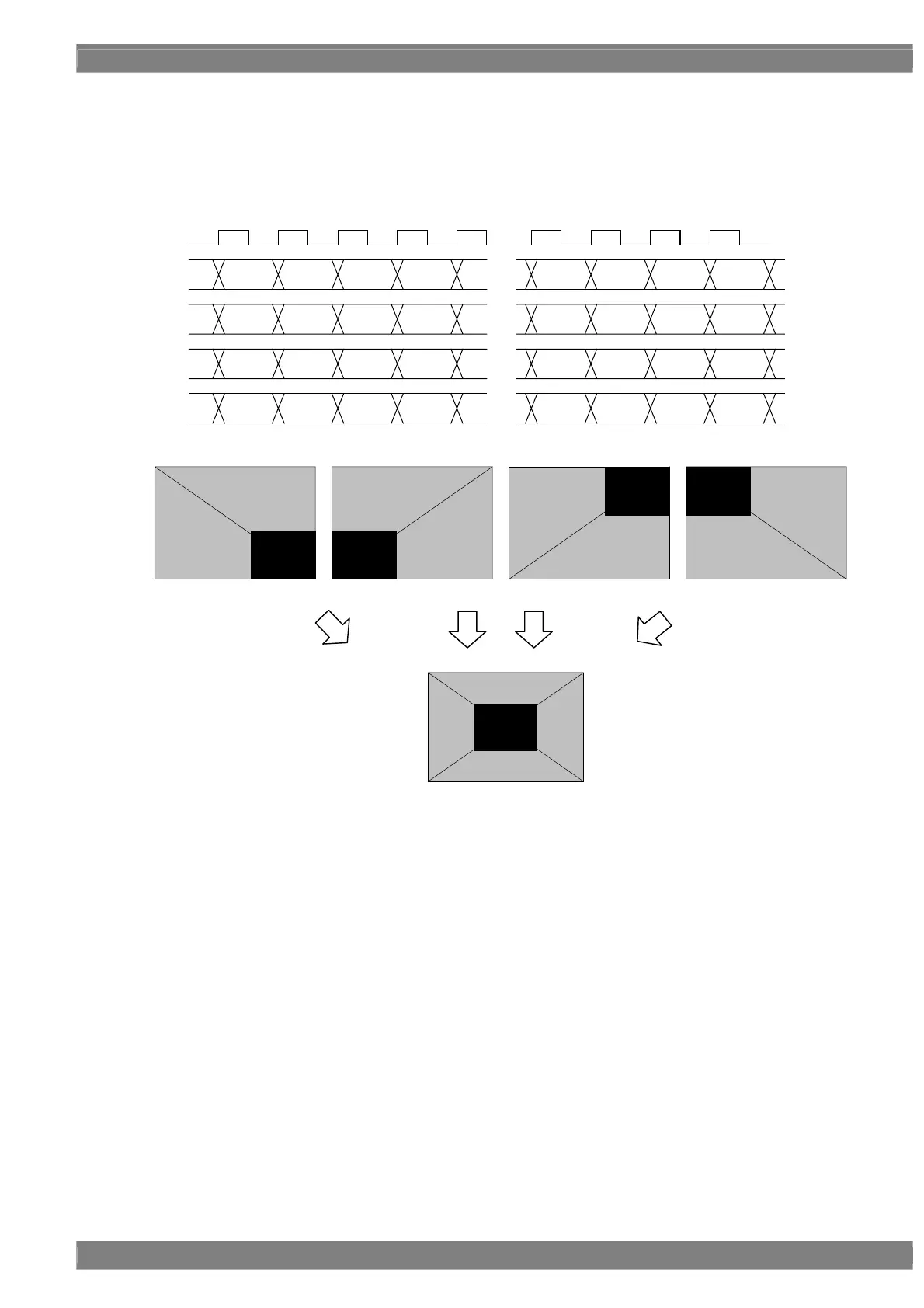

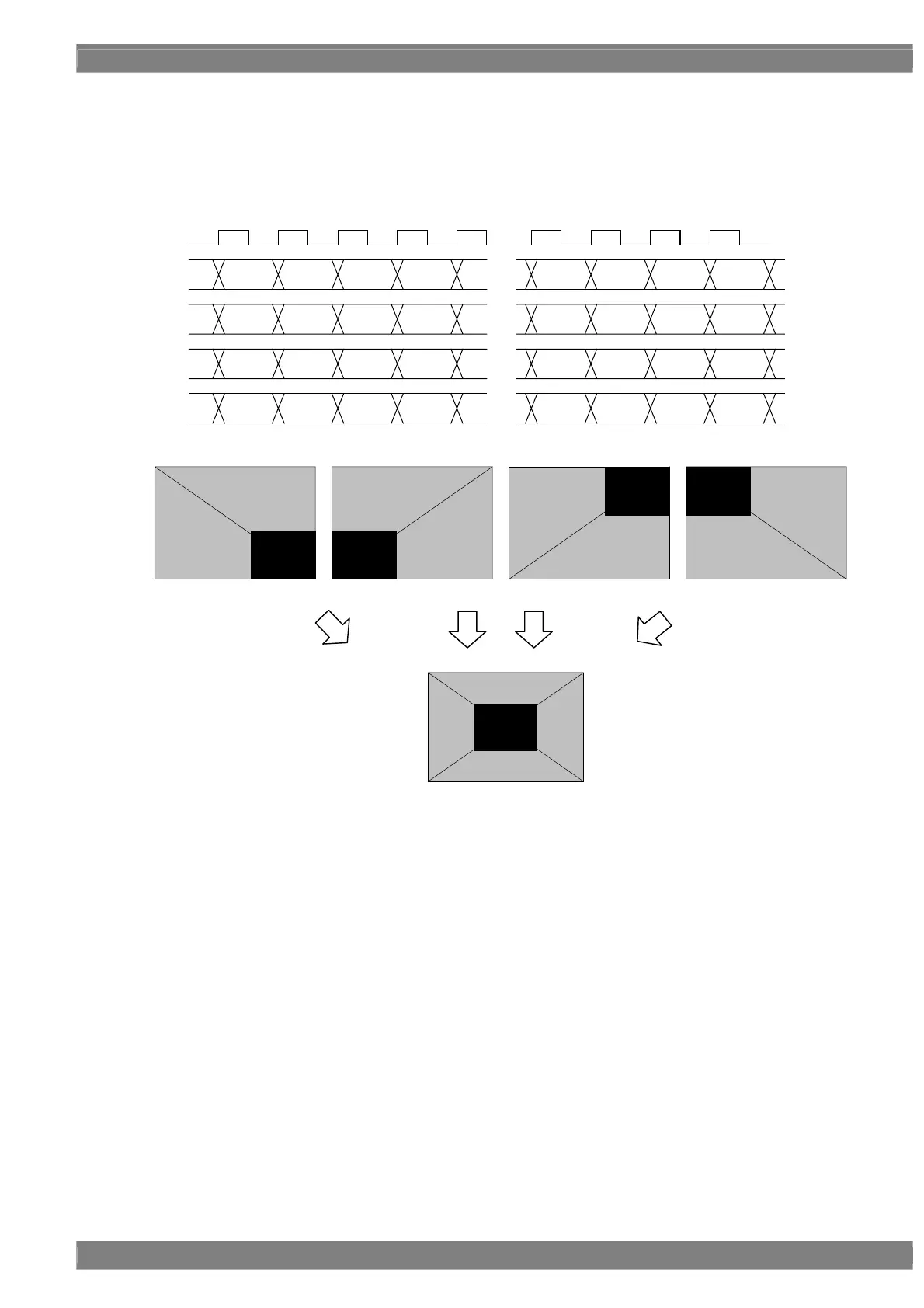

[1] MODE0 (Quad Link ) (screen cross-split-into-4 output)

The screen is split into 4 equal parts using channels 1, 2, 3 and 4.

Given here as an example of the resolution is 4096 × 2048, the dot clock frequency is 592 MHz with the 10 bits

output.

CLK

148MHz

1CH

2CH

3CH

4CH

・・・

L0~L1023

L0~L1023

L1024~L2047

L1024~L2047

D 2044 D 2045 D 2046 D 2047

[9:0] [9:0] [9:0] [9:0]

D 0

[9:0]

D 1 D 2 D 3

・・・

[9:0] [9:0] [9:0]

D 4092

[9:0]

D 4093 D 4094 D 4095

[9:0] [9:0] [9:0]

[9:0]

・・・

[9:0] [9:0] [9:0]

D 2048 D 2049 D 2050 D 2051

D 2044 D 2045 D 2046 D 2047

[9:0] [9:0] [9:0] [9:0]

D 0

[9:0]

D 1 D 2 D 3

・・・

[9:0] [9:0] [9:0]

D 4092

[9:0]

D 4093 D 4094 D 4095

[9:0] [9:0] [9:0]

[9:0]

・・・

[9:0] [9:0] [9:0]

D 2048 D 2049 D 2050 D 2051

1CH 2CH 3CH 4CH

Loading...

Loading...