142

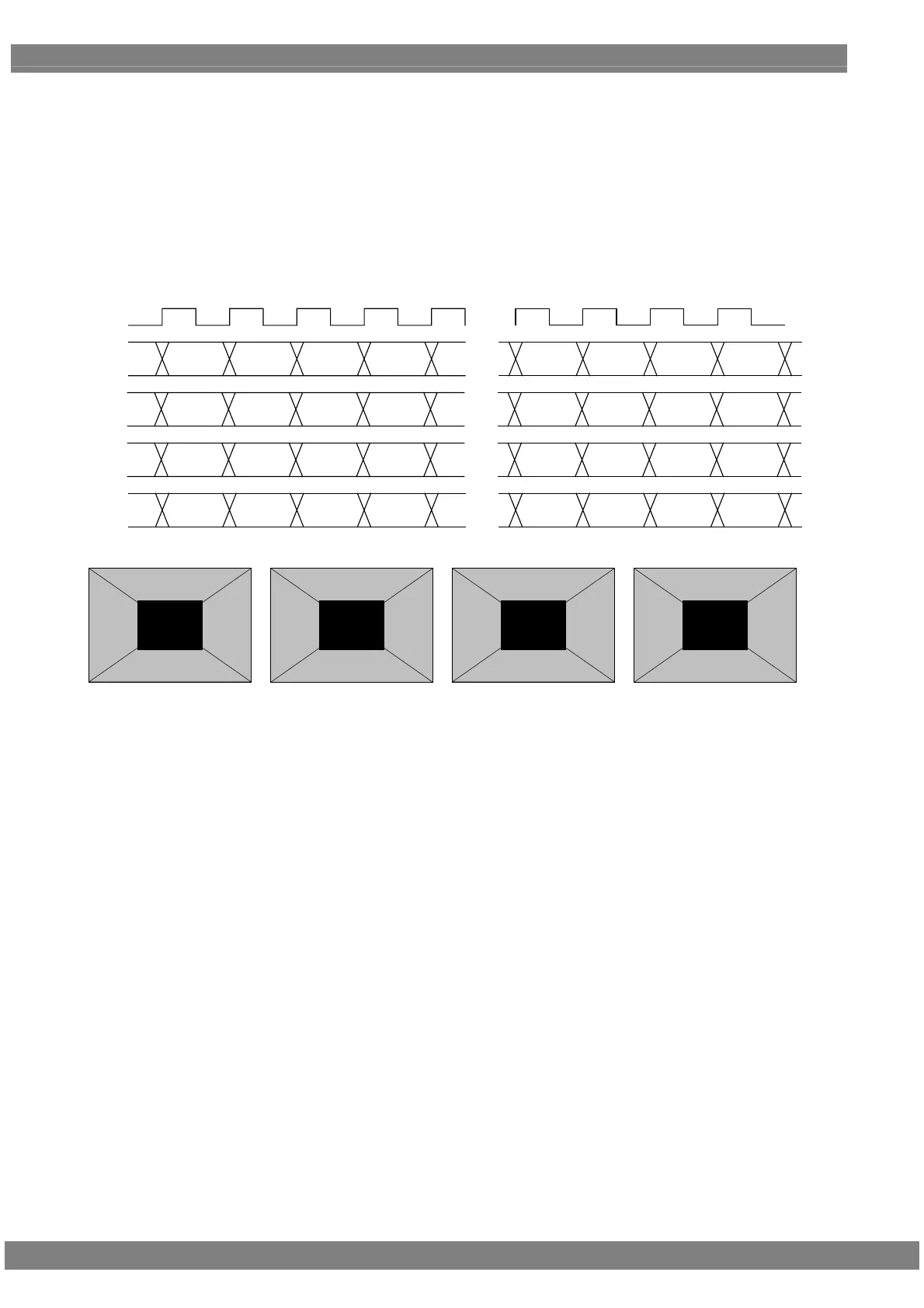

[1] 16Bit (Single Link)

Sixteen-bit images are output using the channel 1 of the Master paired up with the channel 1 of the Slave.

The higher 8 bits are output to channel 1 of the Master and the lower 8 bits to channel 1 of the Slave.

Also, the 16-bit images are output using channel 2 of the Master paired up with channel 2 of the Slave.

The higher 8 bits are output to channel 2 of the Master and the lower 8 bits to channel 2 of the Slave.

Given here as an example for explanatory purposes is a case where the resolution is 1280 × 1024, the dot clock

frequency is 108 MHz with the 16 bits output.

D 0 D 1 D 2 D 3

・・・

・・・

D 1276 D 1277 D 1278 D 1279

CLK

108MHz

D 0 D 1 D 2 D 3

・・・

D 1276 D 1277 D 1278 D 1279

1CH

2CH

3CH

4CH

D 0 D 1 D 2 D 3

・・・

D 1276 D 1277 D 1278 D 1279

D 0 D 1 D 2 D 3

・・・

D 1276 D 1277 D 1278 D 1279

[15:8] [15:8] [15:8] [15:8] [15:8] [15:8] [15:8] [15:8]

[7:0] [7:0] [7:0] [7:0] [7:0] [7:0] [7:0] [7:0]

[15:8] [15:8] [15:8] [15:8] [15:8] [15:8] [15:8] [15:8]

[7:0] [7:0] [7:0] [7:0] [7:0] [7:0] [7:0] [7:0]

Upper Bit [15:8] Lower Bit [7:0] Upper Bit [15:8] Lower Bit [7:0]

1CH 2CH 3CH 4CH

Loading...

Loading...