ED31 [5]

ED30 [5]

ED29 [5]

ED28 [5]

ED27 [5]

ED26 [5]

ED25 [5]

ED24 [5]

ED23 [5]

ED22 [5]

ED21 [5]

ED20 [5]

ED19 [5]

ED18 [5]

ED17 [5]

ED16 [5]

ED15 [5]

ED14 [5]

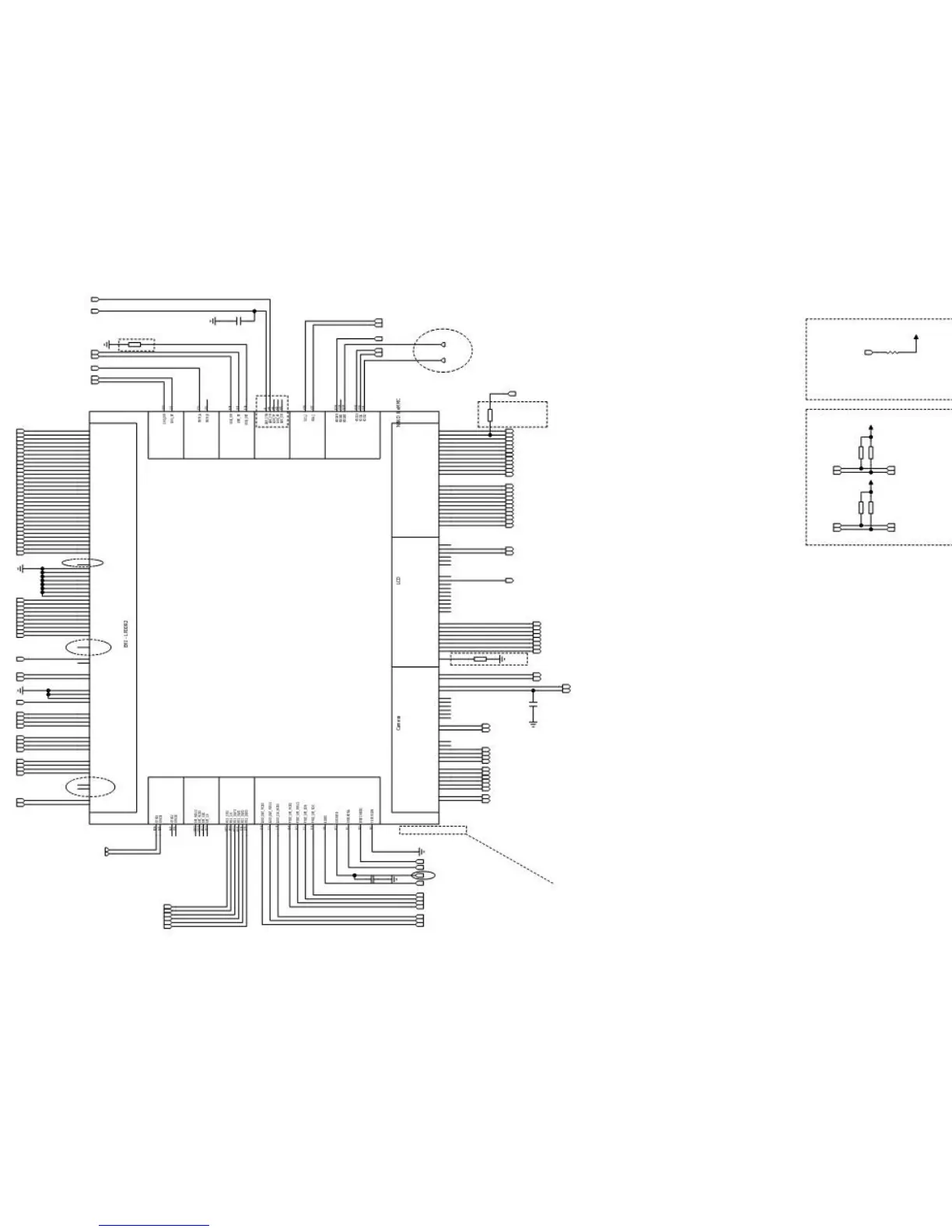

[9] EINT_ALPXS

[8] AUX_IN0

[7] USB_DP

[7] USB_DM

[6] EINT_EAR

[4] C HD_DP

[4] CHD_DM

AG2

AC5

AE5

AD5

AG3

AF5

AC6

AG5

AC16

AE15

AD15

AC14

AG16

AF14

AF16

AF15

AE8

AC9

R7 5.1K/1% Close to BB

90-ohm differential

U3-C

ED31_(DDR2)

ED30_(DDR2)

ED29_(DDR2)

ED28_(DDR2)

ED27_(DDR2)

ED26_(DDR2) BC 1.1 PWM

ED25_(DDR2)

ED24_(DDR2)

ED23_(DDR2)

ED22_(DDR2)

ED21_(DDR2) ED20_(DD R2)

ED19_(DDR2)

ED18_(DDR2)

ED17_(DDR2)

ED16_(DDR2)

ED15_(DDR2)

ED14_(DDR2)

C27 NC SCL_1 [3,8,9]

SDA_1 [3,8,9]

KROW0 [7]

JTAG_TMS_1

KCOL0 [7]

KCOL1 [7] JTAG_TCK_1

Only GPI

ND0_(DDR2)

ND1_(DDR2)

ND2_(DDR2)

ND3_(DDR2)

ND6_(DDR2)

USB ADC I2C Double Key ND8_(DDR2)

ND9_(DDR2)

ND12_(DDR2)

ND13_(DDR2)

ND15_(DDR2)

NCEB_(DDR2) NWRB_(DDR2)

MC0_RSTB_(DDR2)

MC0_DAT7_(DDR2)

MC0_DAT6_(DDR2)

MC0_DAT5_(DDR2)

1

1

MT6571 support JTAG from below :

1. KP (recommand)

2. MC1

3. CAM

for JTAG pin out from MC1/CAM, refer

to HW design notice

TP206

TP207

VIO18_PMU [2,3,4,5,8,9]

R6 HW trapping PIN R211

1K: eMMC

1K NC: NAND

AA4 NLD0 [5]

AB2 NLD1 [5]

W5 NLD2 [5]

Y1 NLD3 [5]

AA3 NLD6 [5]

AA2 NLD8 [5]

Y2 NLD9 [5]

Y4 NLD12 [5]

Y3 NLD13 [5]

W1 NLD15 [5]

Y5

AA5 NCEB

[5 ] [5 ]

NWRB

AC1 NLD10 [5]

AE3 NALE [5]

AD3 NCLE [5]

AD2 [5]

HW trapping PIN for JTAG debug from KP(serial)

VIO18_PMU

[2,4] SIM1_SCLK R8 NC

Normal : NC

JTAG : 4.7K

Reserve R footprint for JTAG

debugging

(please refer to HW design notice)

VIO18_PMU

R9 R10

Power by CTP, MEMS sensor

2.2K 2.2K

[3,8,9] SDA_1 SDA_1 [3,8,9]

[3,8,9] SCL_1 SCL_1 [3,8,9]

VCAMD_IO_PMU

ED13

ED12

ED11

ED10

ED9

ED8

ED7

ED6

[5]

[5]

[5]

[5]

[5]

[5]

[5]

[5]

AD8

AD7

AG8

AF7

AF6

AC8

AF11

AG9

ED13_(DDR2)

ED12_(DDR2)

ED11_(DDR2)

ED10_(DDR2)

ED9_(DDR2)

ED8_(DDR2)

ED7_(DDR2)

ED6_(DDR2)

MC0_DAT4_(DDR2)

MC0_DAT3_(DDR2)

MC0_DAT2_(DDR2)

MC0_DAT1_(DDR2)

MC0_DAT0_(DDR2)

MC0_CK_(DDR2)

MC0_CMD_(DDR2)

AE2

AF2

AF1

AC3

AC2

AD1

AF3

NLD4

NLD 5 NLD 7 [5] [5]

NLD14 [5]

NLD11 [5]

GPIO74 [5]

NREB [5]

NRNB [5]

[3,9]

[3,9]

SDA_0

SCL_0

R11

2.2K

R12

2.2K

Power by CAM_IO

SDA_0 [3,9]

[3,9]

ED5 [5] AD10

ED4 [5] AE13

ED3 [5] AG12

ED2 [5] AD13

ED1 [5] AF10

ED0 [5] AG13

for DDR2 : AG25 must NC AG25

AF23 AF21

AF17

AF24

AF22

AE22

AG24

AC19

EA9 [5] AD23

EA8 [5] AG22

EA7 [5] AE21

EA6 [5] AD22

EA5 [5] AC20

EA4 [5] A F20

EA3 [5] A F19

EA2 [5] AC18

EA1 [5] A F18

EA0 [5] AE18

for DDR2 : AF26 must NC AF26

EVREF [5] AD11

AC17

ECS0_B [5] AG21

ECS1_B [5] AE24

AD18

AG19

AG18

ECKE [5] AF25

EDQM0 [5] AE12

EDQM1 [5] AD12

EDQM2 [5] AC13

EDQM3 [5] AE7

EDQS0 [5] AA13

EDQS1 [5] AB9

EDQS2 [5] AB14

EDQS3 [5] AA8

EDQS0_B [5] A B13

EDQS1_B [5] AA9

EDQS2_B [5] AA 14

EDQS3_B [5] AB8

AB18

for DDR2 : AA18+AB18 must NC AA18

EDCLK [5] AA19

EDCLK_B [5] A B19

ED5_(DDR2)

ED4_(DDR2)

ED3_(DDR2)

ED2_(DDR2)

ED1_(DDR2)

ED0_(DDR2)

EA18_(DDR2)

EA17_(DDR2)

EA16_(DDR2) EA15_(DDR2)

EA14_(DDR2)

EA13_(DDR2)

EA12_(DDR2)

EA11_(DDR2)

EA10_(DDR2)

EA9_(DDR2)

EA8_(DDR2)

EA7_(DDR2)

EA6_(DDR2)

EA5_(DDR2)

EA4_(DDR2)

EA3_(DDR2)

EA2_(DDR2)

EA1_(DDR2)

EA0_(DDR2)

ERESET

VREF0

VREF1

ECS0_B_(DDR2)

ECS1_B_(DDR2)

EWR_B_(DDR2)

ERAS_B_(DDR2)

ECAS_B_(DDR2)

ECKE_(DDR2)

EDQM0_(DDR2)

EDQM1_(DDR2)

EDQM2_(DDR2)

EDQM3_(DDR2)

EDQS0_(DDR2)

EDQS1_(DDR2)

EDQS2_(DDR2)

EDQS3_(DDR2)

EDQS0_B

EDQS1_B

EDQS2_B

EDQS3_B

EDCLK0

EDCLK0_B UART

EDCLK1

EDCLK1_B

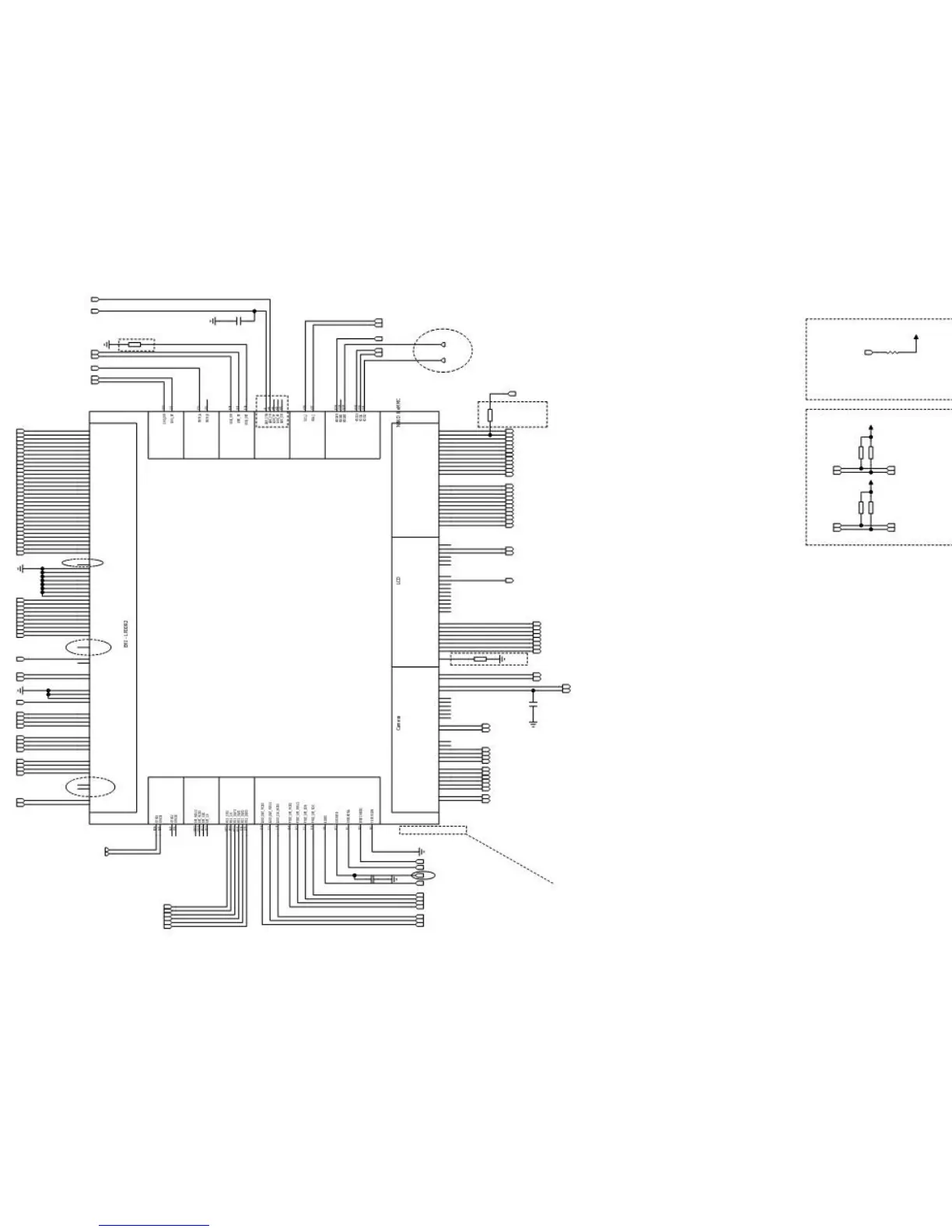

MT6571_BB

SPI MSDC SYS Ctrl

LPCEB

LPTE

LRSTB

LPRDB LPA0

LPWRB

LPD9

LPD8

LPD7

LPD6

LPD5

LPD4

LPD3

LPD2

LPD1

LPD0

TDN2

TDP2

TDN0

TDP0

TDN1 TDP1

TCN

TCP

MIPI_VRT

SCL_0

SDA_0

CMPCLK

CMMCLK

RDN0

RDP0

RDN1 RDP1

RCN

RCP

CMRST

CMPDN

CMDAT0

CMDAT1

CMDAT2

CMDAT3

CMDAT4

CMDAT5

RDN0_A

RDP0_A

RDN1_A

RDP1_A

RCN_A

RCP_A

CMRST2

CMPDN2

AE25

AC24 DSI_TE [8]

AD24 AC25

DSI_LRSTB [8]

AD26

AD25

AC23

AB23 LCM_BLPWM [8]

AB22

AA22

Y22

W22

W23

V23

V24

AB24 100-ohm differential

AA25 MIPI_TDN2

Y25 MIPI_TDP2

Y26 MIPI_TDN0

W26 MIPI_TDP0

U25 U26

MIPI_TDN1

W25

MI PI_T DP1 M IPI_T CN

V25 MIPI_TCP

U24 R5 1.5K Close to BB IC

MIPI_VRT

N21 SCL_0

M21 SDA_0

L23

K24

R21

P21 C34

P20 P19

NC

U22

V22

K25 M_CMRST [9]

K23 M_CMPDN [9]

P25

N25

N26 CMDAT2 [9]

M26 CMDAT3 [9]

M25 CMDAT4 [9]

P24 CMDAT5 [9]

R26 CMHREF [9]

R25 CMVSYNC [9]

P22 CMDAT6 [9]

P23 CMDAT7 [9]

T22 CMDAT8 [9]

R22 CMDAT9 [9]

N22 SUB_CMRST2 [9]

M22 SUB _CMPDN2 [9]

SCL_0

[8]

[8]

[8]

[8]

[8]

[8 ] [8 ]

[8]

[3,9]

[3,9]

CMPCLK [9]

CMMCLK [9]

MT6571_LPDDR2_V12_20131219

UART1 : AP UART

UTXD1

1

UTXD1

URXD1 1

URXD1

WATCHDOG [4,5]

PMIC_SRC LKENA [4]

C30 NC RESETB [4] 72没加C

EINT_PMIC [4]

Please make sure the ball map is

PMIC_SP I_SCK

[4]

PMIC_SP I_CS [4,5] match to the MCP type you selected

PMIC_SP I_MISO [4]

[8] MC1CMD PMIC_SP I_MOSI [4]

[8] MC1CK

[8] [8] MC1DAT0

AUD_CLK

[4] For other memory pin mux, please refer

[8]

MC1DAT1 MC1DAT2

AUD_MISO [4]

[8] MC1DAT3 AUD_MOSI [4] to Design Notice "DDR1/DDR2 Pin Mux"

Loading...

Loading...