- 4 -

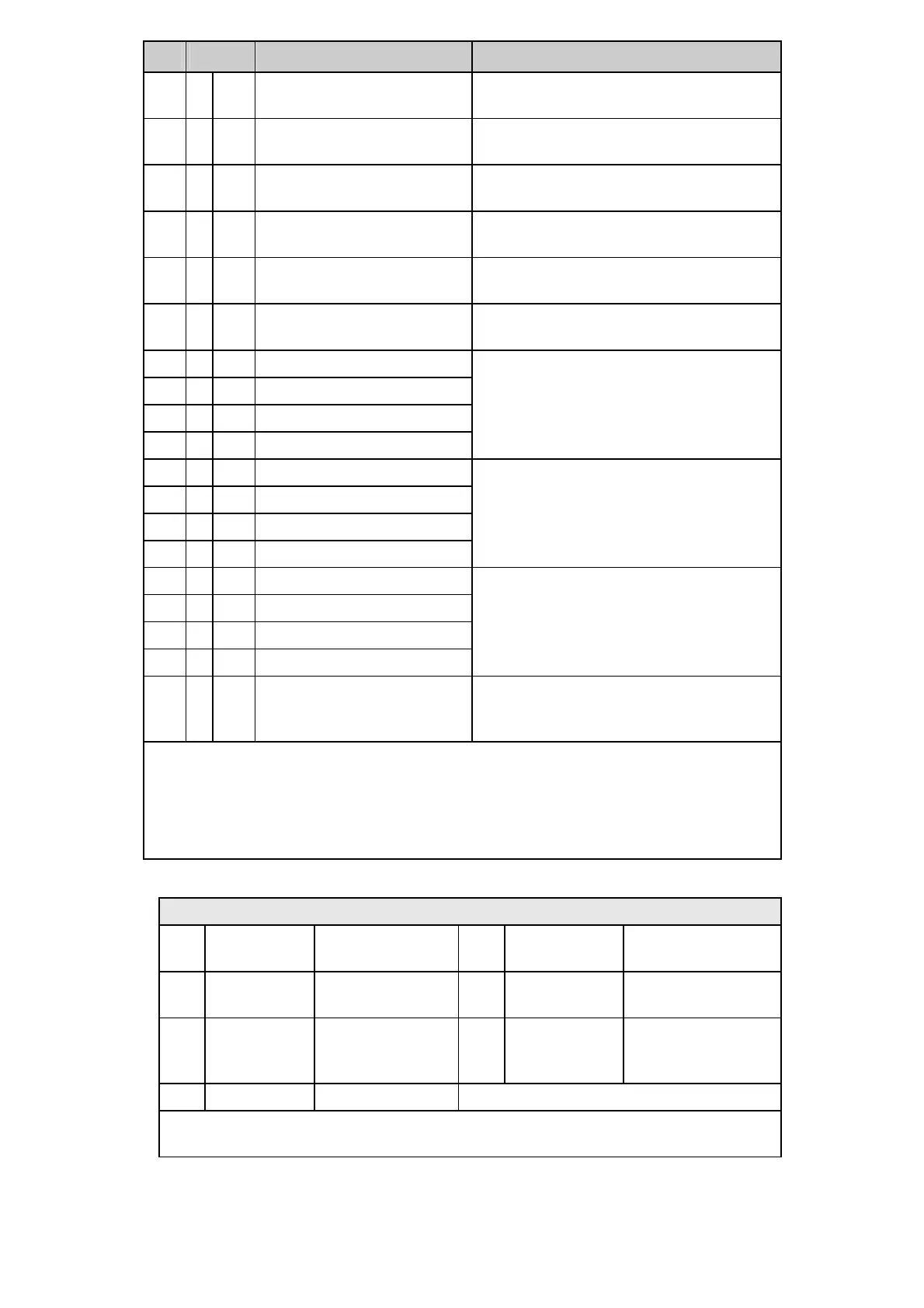

CR# Attrib. Register name Explanation

#40 O R/W

Function: Set value changing

prohibited

Prohibit set value changing in CH1 ~ CH4.

Default= H’0000.

#41 X R/W

Function: Save all the set

values

Save all the set values. Default =H’0000.

#42 X R/W

Function: Return to default

setting

Set all values to default setting. Default =

H’0000

#43 X R Error status

Register for storing all error status. Refer to

table of error status for more information.

#100 O R/W

Function: Enable/Disable limit

detection

Enable/Disable the upper and lower bound

detection function. Default= H’0000.

#101 X R/W Upper and lower bound status

Display the upper and lower bound value.

Default =H’0000.

#102 O R/W Set value of CH1 upper bound

#103 O R/W Set value of CH2 upper bound

#104 O R/W Set value of CH3 upper bound

#105 O R/W Set value of CH4 upper bound

Set value of CH1~CH4 upper bound. Default

= K32000.

#108 O R/W Set value of CH1 lower bound

#109 O R/W Set value of CH2 lower bound

#110 O R/W Set value of CH3 lower bound

#111 O R/W Set value of CH4 lower bound

Set value of CH1~CH4 lower bound. Default

= K-32000.

#114 O R/W Output update time of CH1

#115 O R/W Output update time of CH2

#116 O R/W Output update time of CH3

#117 O R/W Output update time of CH4

Set value of CH1~CH4 lower bound. Default

=H’0000.

#118 O R/W LV output mode setting

Set the output mode of CH1~CH4 when the

power is at LV (low voltage) condition.

Default= H’0000.

Symbols:

O: When CR#41 is set to H’5678, the set value of CR will be saved.

X: set value will not be saved.

R: able to read data by using FROM instruction.

W: able to write data by using TO instruction.

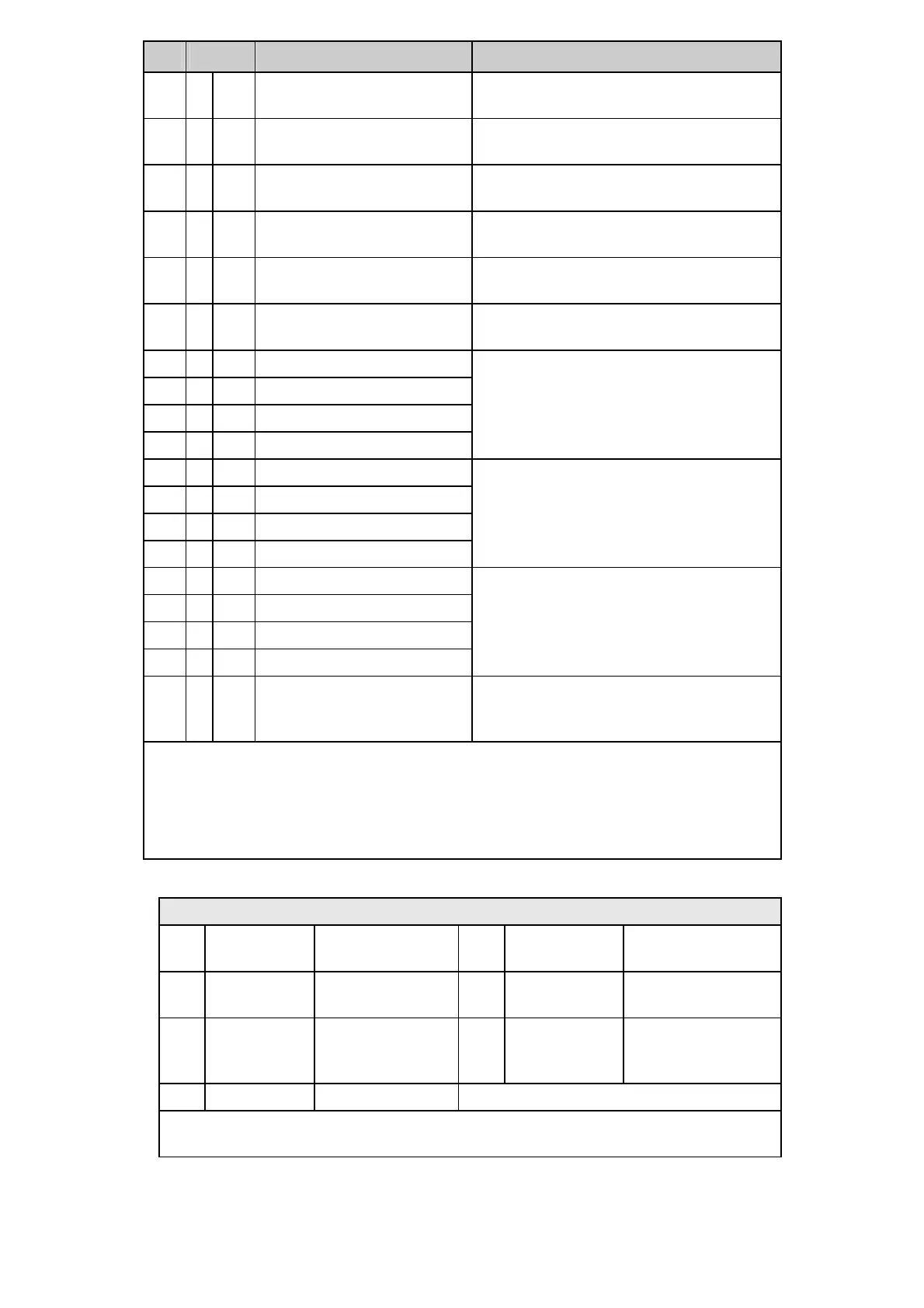

ϡ!CR#43: Error status value. See the table below:

Description

bit0 K1 (H’1) Power supply error bit11 K2048(H’0800)

Upper / lower bound

setting error

bit1 K2 (H’2) Hardware error bit12 K4096(H’1000)

Set value changing

prohibited

bit2 K4 (H’4)

Upper / lower

bound error

bit13 K8192(H’2000)

Communication

breakdown on next

module

bit9 K512(H’0200) Mode setting error

Note: Each error status is determined by the corresponding bit (b0 ~ b13) and there may be more

than 2 errors occurring at the same time. 0 = normal; 1 = error

Explanation on Special Registers D9900~D9999

When DVP-ES2 MPU is connected with modules, registers D9900~D9999 will be

Loading...

Loading...