1 - 1 1 - 1

MELSEC-Q

1 OVERVIEW

1 OVERVIEW

This User's Manual describes the specifications, handling and programming method

for the QD62, QD62E and QD62D high-speed counter modules (QD62 (E/D)) used

together with the MELSEC-Q series CPUs.

The QD62(E/D) modules are available with the following I/O types, maximum counting

speeds and number of channels.

Item QD62 QD62E QD62D

I/O type

DC input sinking

output

DC input sourcing

output

Differential input

sinking output

Maximum counting speed 200 kPPS 500 kPPS

Number of channels 2 channels

The QD62(E/D) modules have the following input methods for 1 phase/2 phase pulse input:

• Phase 1 pulse input multiple of 1 • Phase 1 pulse input multiple of 2 • CW/CCW

• Phase 2 pulse input multiple of 1 • Phase 2 pulse input multiple of 2

• Phase 2 pulse input multiple of 4

See Section 5.1 for details on the input methods.

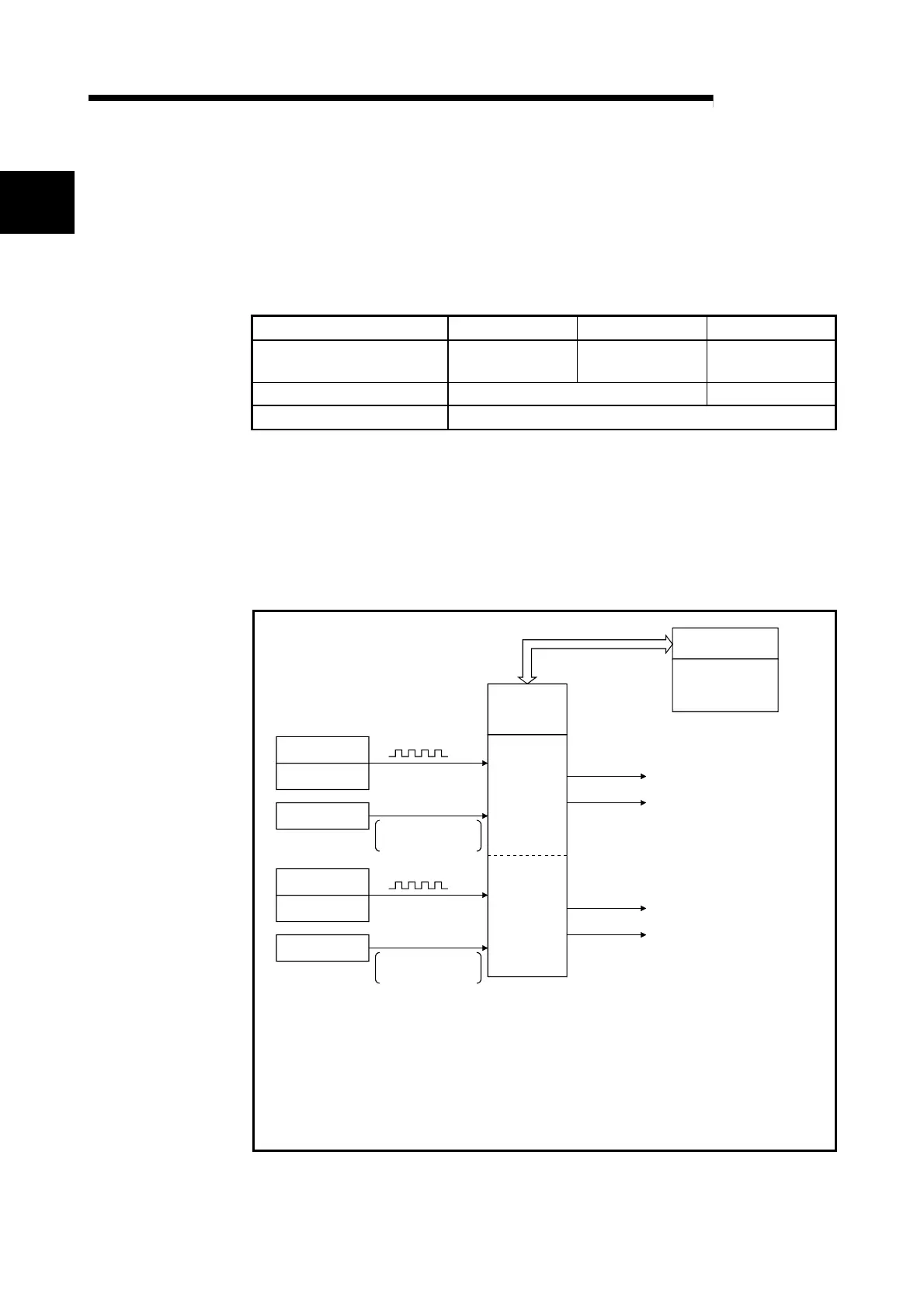

An overview of QD62 (E/D) operation is shown in the figure below.

Pulse generator

Encoder

Controller

Pulse

External

control signal

Preset counter

function selection

2)

1)

3) Coincidence signal output

(2 points)

CH1

Pulse generator

Encoder

Controller

Pulse

External

control signal

Preset counter

function selection

4)

3)

3) Coincidence signal output

(2 points)

CH2

QD62(E/D)

QCPU (Q mode)

Programmable

controller CPU

Buffer memory

read/write

4) I/O signal

1) Counts the pulses to be input to the QD62 (E/D).

2) Preset or counter function can be selected with an external control signal.

3) The present count value and the coincidence output point setting value can be

compared to output a coincidence signal.

4) Using the sequence program, the I/O signal and buffer memory status of the

QD62 (E/D) can be verified.

Also, count start/stop, preset, and counter function can be selected.

1

Loading...

Loading...