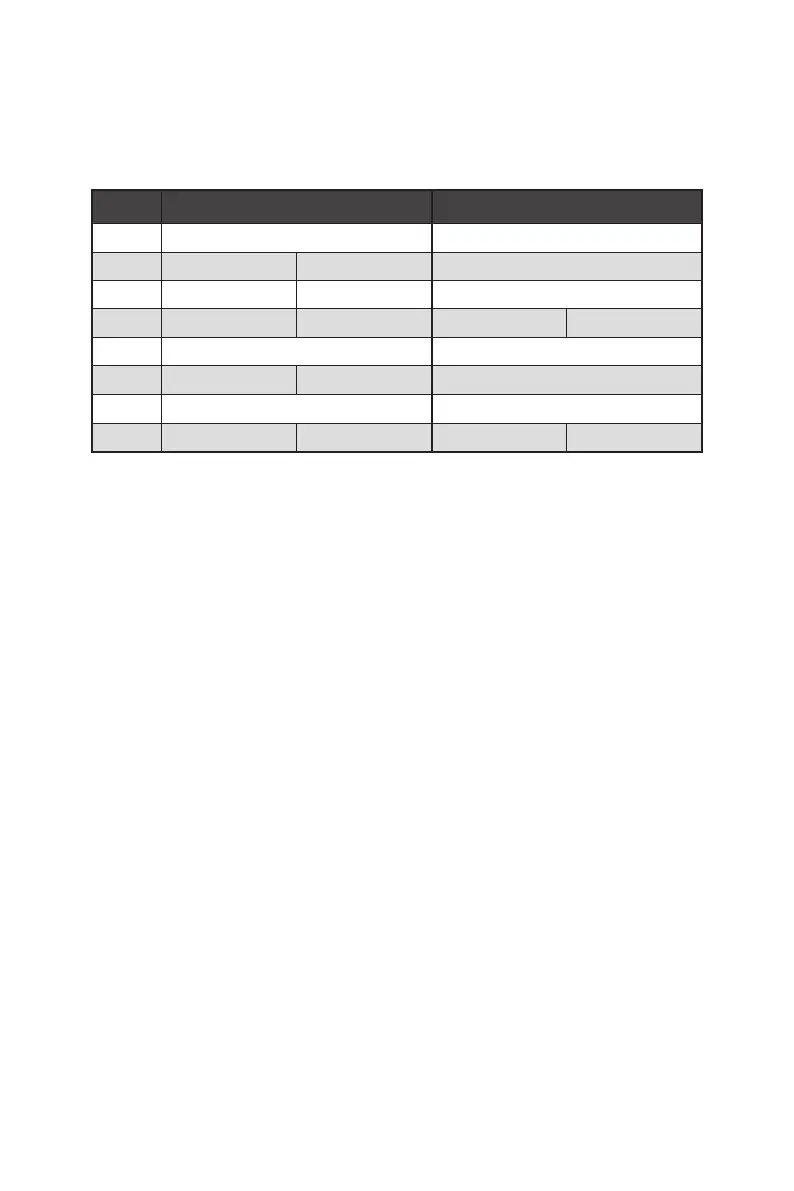

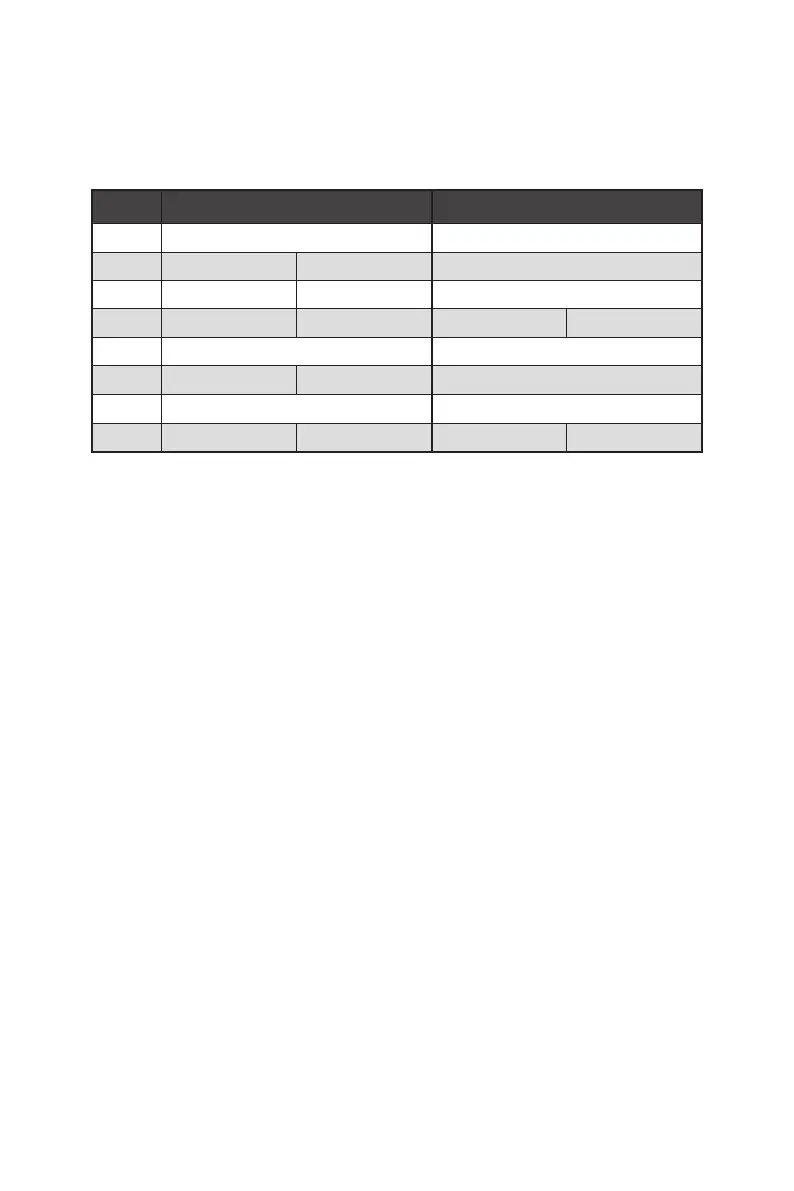

20

@ 4.0/ 3.0 x16* @ 4.0/ 3.0 x8*

— 3.0 x1 3.0 x1

— 3.0 x1 3.0 x1

— @ 3.0 x4 — @ 3.0 x4

M2_1 4.0/ 3.0 x4* 4.0/ 3.0 x4*

M2_2 3.0 x2 4.0/ 3.0 x4*

M2_3 3.0 x2** 4.0/ 3.0 x4*

/

**

M2_4 3.0 x4 3.0 x4

PCIe

M.2 SATA

CPU

AMD Ryzen™ 5000 & 3000

AMD Ryzen™ 4000-G

Loading...

Loading...