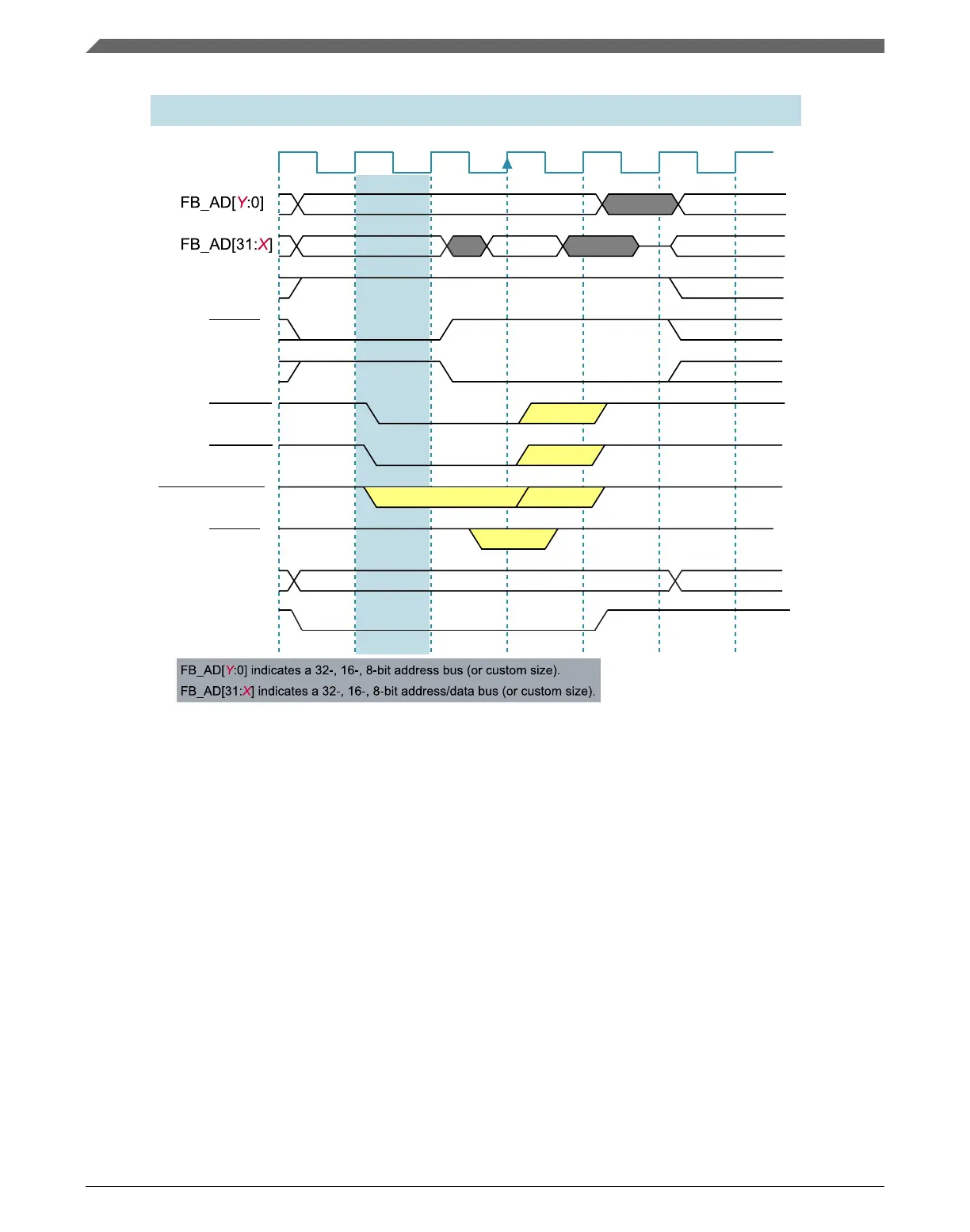

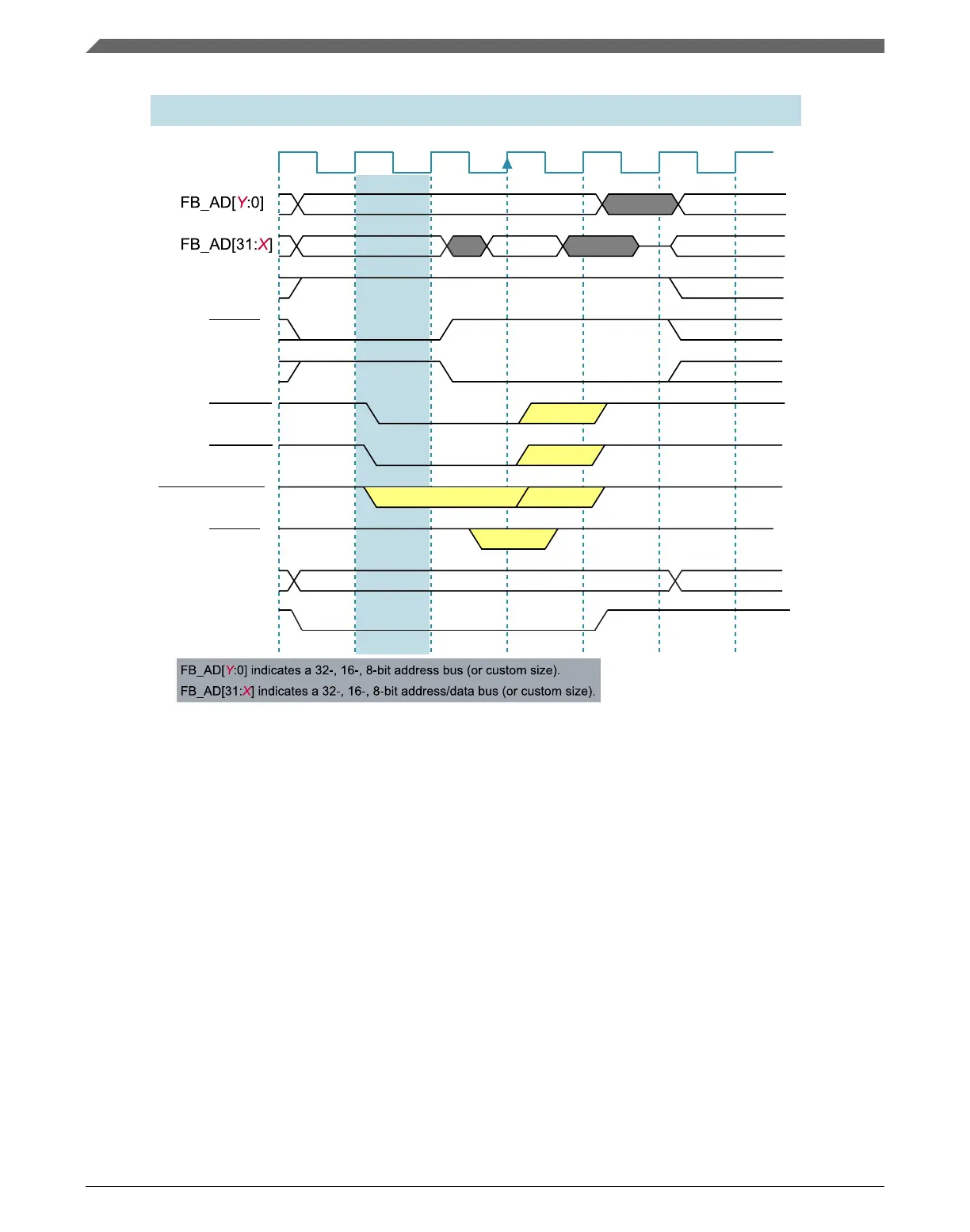

Address

Address Data

TSIZ

AA=1

AA=0

AA=1

AA=0

FB_CLK

FB_RW

FB_TS

FB_ALE

FB_CSn

FB_OEn

FB_BE/BWEn

FB_TA

FB_TSIZ[1:0]

BEM=1

BEM=0

32-bit Read with Extended Transfer start and 1 wait state

S2 S3 S0ASS0 S1

TIP

S2 S3 S0ASS0 S1

ReadExtendTS1WS.svg

Figure 31-29. Read-Bus Cycle with CSCRn[EXTS] = 1 (One Wait State)

31.4.14

Bus errors

These types of accesses cause a transfer to terminate with a bus error:

• A write to a write-protected address range

• An access whose address is not in a range covered by a chip-select

• An access whose address is in a range covered by more than one chip-selects

• A write to a reserved address in the memory map

• A write to a reserved field in the CSPMCR

• Any FlexBus accesses when FlexBus is secure

Functional description

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

738 NXP Semiconductors

Loading...

Loading...