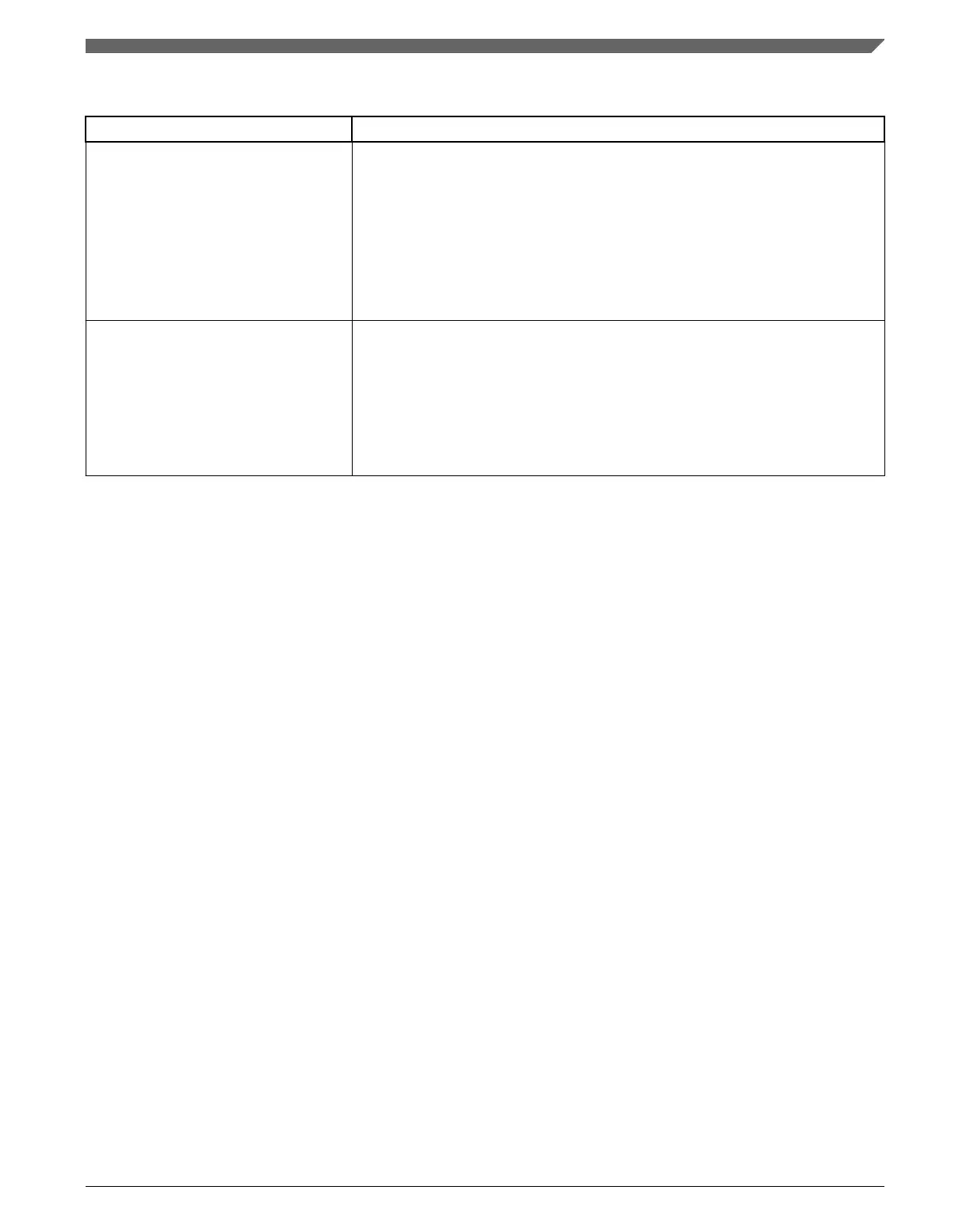

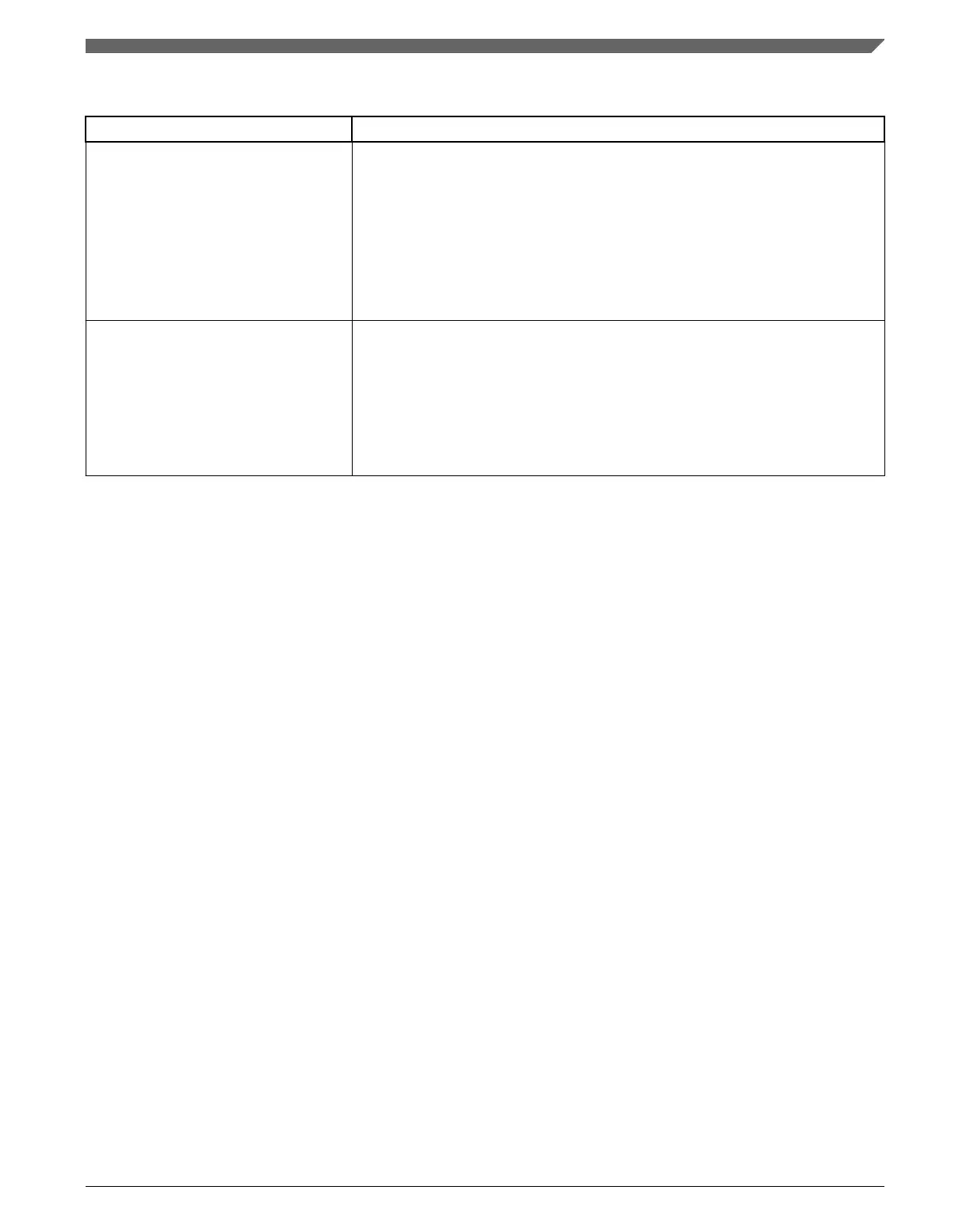

Table 39-7. CnV register update (continued)

When Then CnV register is updated

• If the selected mode is Output Compare, then CnV register is updated on the

next FTM counter change, end of the prescaler counting, after CnV register

was written.

• If the selected mode is EPWM, then CnV register is updated after CnV

register was written and the FTM counter changes from MOD to CNTIN. If

the FTM counter is at free-running counter mode then this update occurs

when the FTM counter changes from 0xFFFF to 0x0000.

• If the selected mode is CPWM, then CnV register is updated after CnV

register was written and the FTM counter changes from MOD to (MOD –

0x0001).

• CLKS[1:0] ≠ 0:0, and

• FTMEN = 1

According to the selected mode, that is:

• If the selected mode is output compare then CnV register is updated

according to the SYNCEN bit. If (SYNCEN = 0) then CnV register is updated

after CnV register was written at the next change of the FTM counter, the

end of the prescaler counting. If (SYNCEN = 1) then CnV register is updated

by the C(n)V and C(n+1)V register synchronization.

• If the selected mode is not output compare and (SYNCEN = 1) then CnV

register is updated by the C(n)V and C(n+1)V register synchronization.

39.4.11 PWM synchronization

The PWM synchronization provides an opportunity to update the MOD, CNTIN, CnV,

OUTMASK, INVCTRL and SWOCTRL registers with their buffered value and force the

FTM counter to the CNTIN register value.

Note

The legacy PWM synchronization (SYNCMODE = 0) is a

subset of the enhanced PWM synchronization (SYNCMODE =

1). Thus, only the enhanced PWM synchronization must be

used.

39.4.11.1

Hardware trigger

Three hardware trigger signal inputs of the FTM module are enabled when TRIGn = 1,

where n = 0, 1 or 2 corresponding to each one of the input signals, respectively. The

hardware trigger input n is synchronized by the system clock. The PWM synchronization

with hardware trigger is initiated when a rising edge is detected at the enabled hardware

trigger inputs.

If (HWTRIGMODE = 0) then the TRIGn bit is cleared when 0 is written to it or when the

trigger n event is detected.

Chapter 39 FlexTimer Module (FTM)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 973

Loading...

Loading...