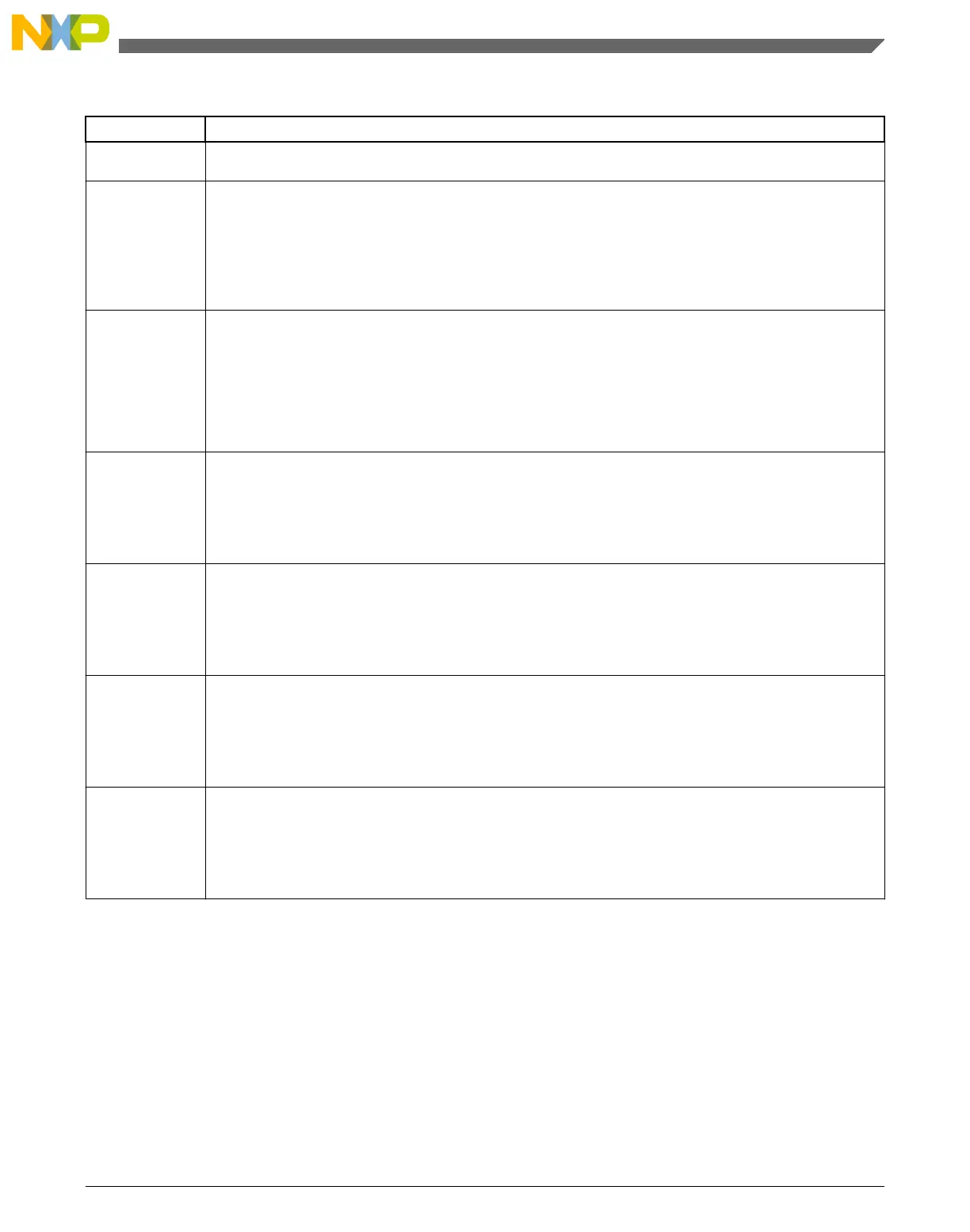

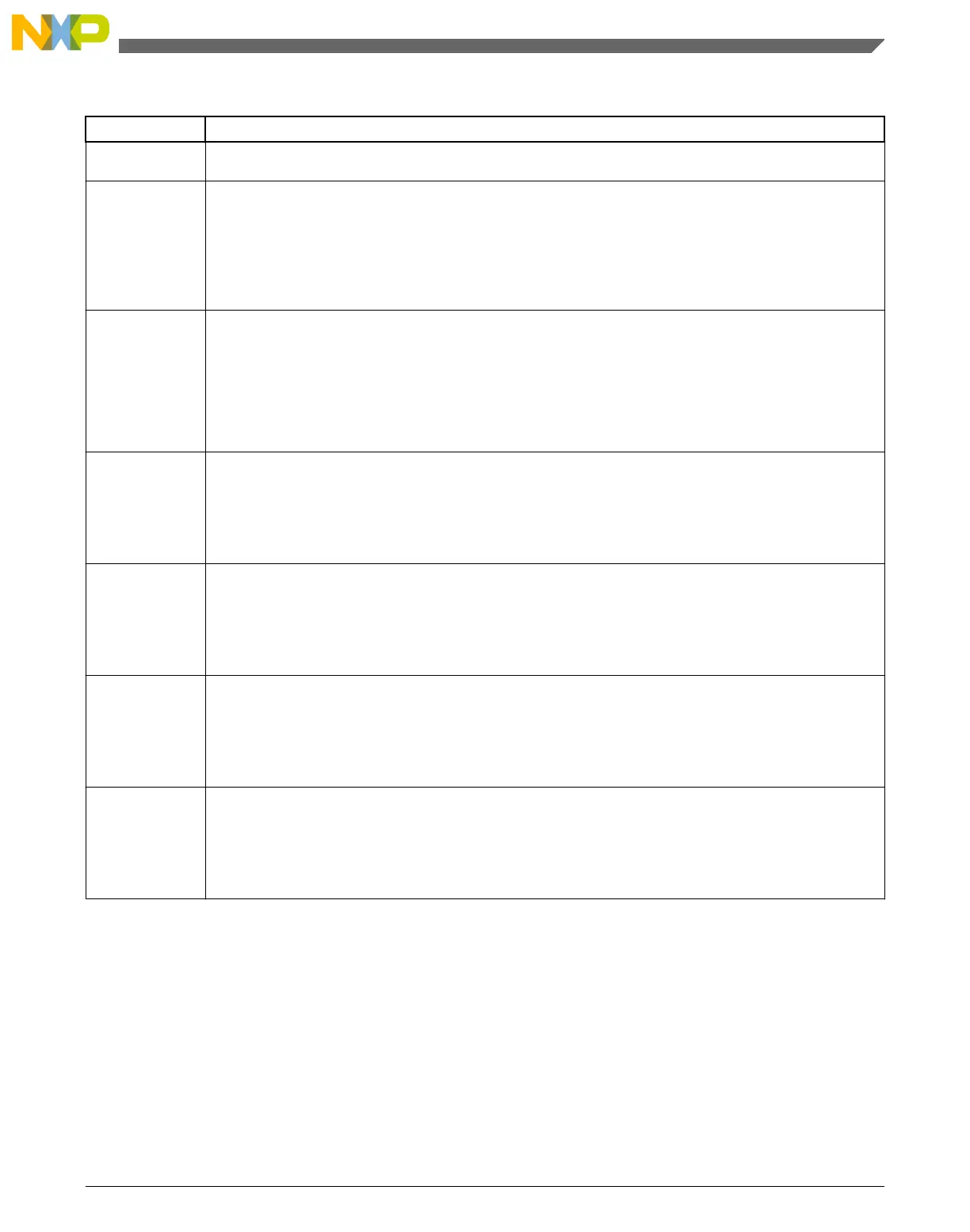

UARTx_C3 field descriptions (continued)

Field Description

such as when it is used to generate mark or space parity, it need not be written each time UART_D is

written.

5

TXDIR

TxD Pin Direction in Single-Wire Mode

When the UART is configured for single-wire half-duplex operation (LOOPS = RSRC = 1), this bit

determines the direction of data at the TxD pin.

0 TxD pin is an input in single-wire mode.

1 TxD pin is an output in single-wire mode.

4

TXINV

Transmit Data Inversion

Setting this bit reverses the polarity of the transmitted data output.

NOTE: Setting TXINV inverts the TxD output for all cases: data bits, start and stop bits, break, and idle.

0 Transmit data not inverted.

1 Transmit data inverted.

3

ORIE

Overrun Interrupt Enable

This bit enables the overrun flag (OR) to generate hardware interrupt requests.

0 OR interrupts disabled; use polling.

1 Hardware interrupt requested when OR is set.

2

NEIE

Noise Error Interrupt Enable

This bit enables the noise flag (NF) to generate hardware interrupt requests.

0 NF interrupts disabled; use polling).

1 Hardware interrupt requested when NF is set.

1

FEIE

Framing Error Interrupt Enable

This bit enables the framing error flag (FE) to generate hardware interrupt requests.

0 FE interrupts disabled; use polling).

1 Hardware interrupt requested when FE is set.

0

PEIE

Parity Error Interrupt Enable

This bit enables the parity error flag (PF) to generate hardware interrupt requests.

0 PF interrupts disabled; use polling).

1 Hardware interrupt requested when PF is set.

Chapter 40 Universal Asynchronous Receiver/Transmitter (UART1 and UART2)

KL25 Sub-Family Reference Manual, Rev. 3, September 2012

Freescale Semiconductor, Inc. 759

Loading...

Loading...