Flash Memory

MPC5606S Microcontroller Reference Manual, Rev. 7

666 Freescale Semiconductor

Table 17-71 illustrates flash access and protection by master. Note that PFAPR’s initial value is loaded

from shadow flash location 0x20 3E00 after reset. The “Master” numbers correspond to the crossbar

masters, which for this device are:

• Master 0: e200z0 core instructions

• Master 1: e200z0 core data

• Master 2: eDMA

• Master 4: DCU

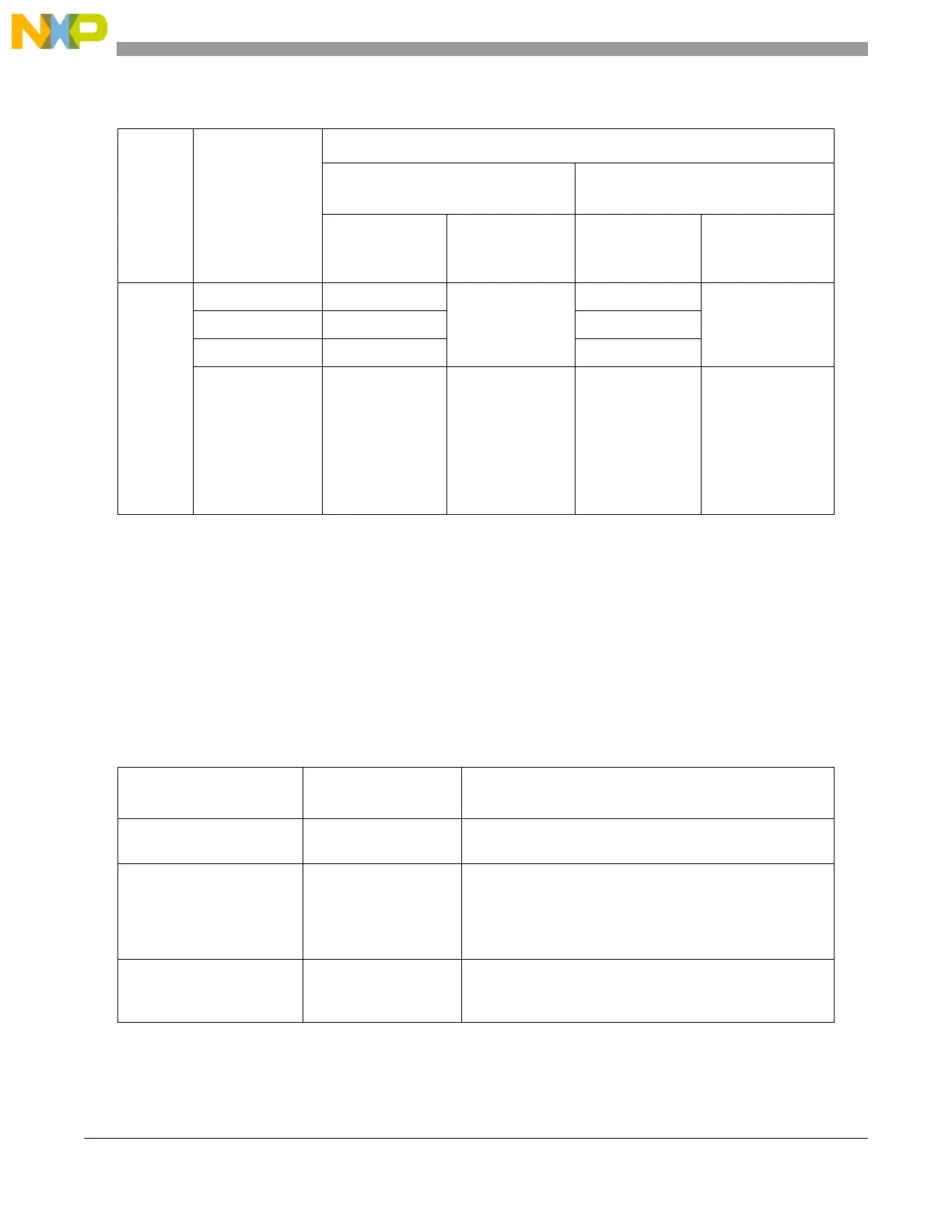

Array

Access

(for 64

MHz)

Read Wait States BK0_RWSC = 2 Values are system

clock frequency

dependent

BK1_RWSC = 2 Values are system

clock frequency

dependent

Write Wait States BK0_WWSC = 2 BK1_WWSC = 2

Adv. Pipeline Ctl. BK0_APC = 2 BK1_APC = 2

Read While Write

Ctl.

BK0_RRWC = 0 Terminate RWW

attempt with error

response.

Assumes software

must first check if

any program or

erase commands

are in progress.

BK1_RRWC = 0 Terminate RWW

attempt with error

response. Assumes

software must first

check if any

program or erase

commands are in

progress.

1

Result value for recommendations in PFCR0 = 0x1084_126E, PFCR1 = 0x1084_0101

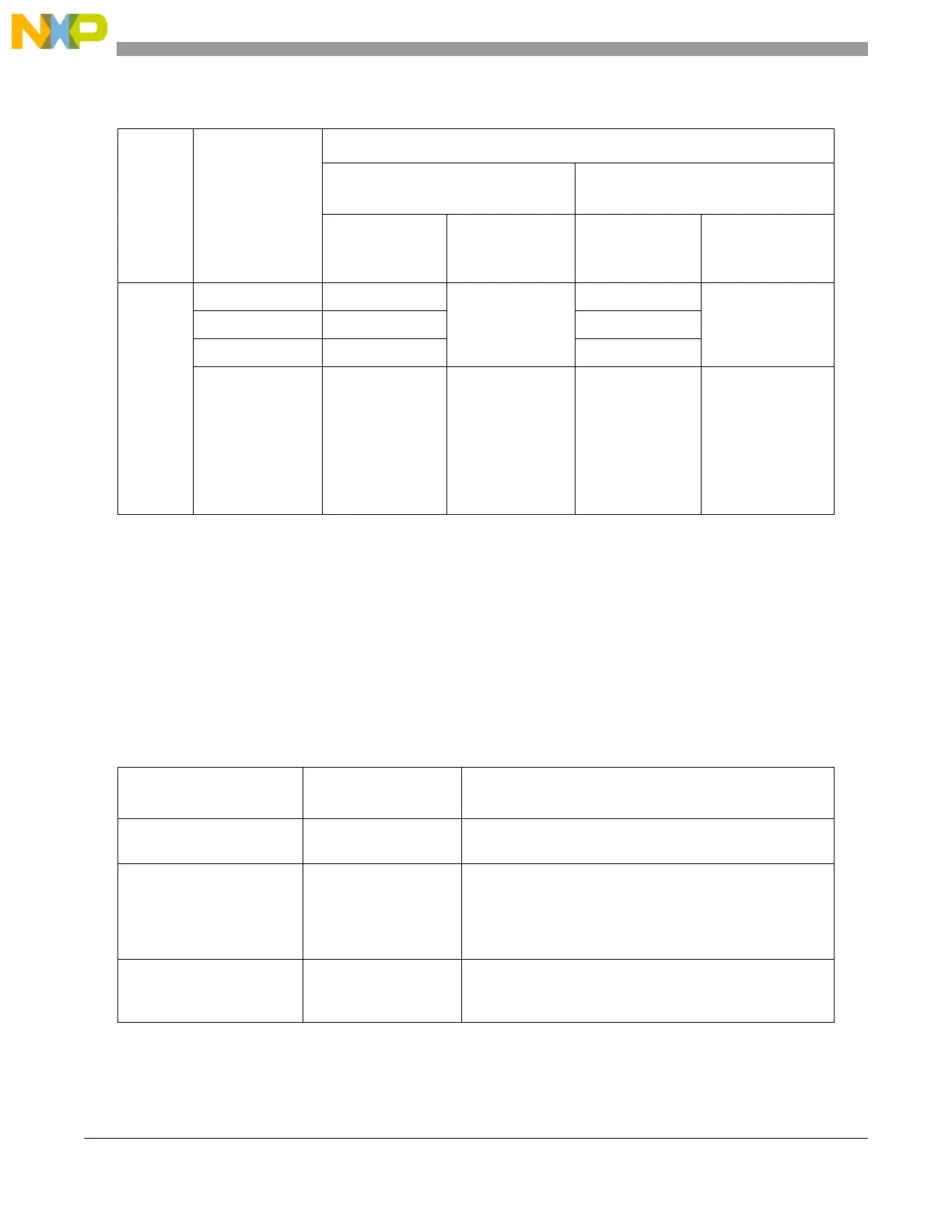

Table 17-71. Access and protection setting recommendations

1

1

Result value for recommendations in PFAPR = 0x03F2 005D

Parameter

Parameter Symbol

in register PFAPR

Comments

Arbitration mode ARBM = 3 Start with round-bin (2 or 3).Change to fixed priority if

application analysis indicates improved performance.

Master n Prefetch Disable MnPFD = 0 for core

instructions, eDMA and

DCU; 1 for core data

Start with allowing prefetching (0) for core instructions since

it is expected the core will have mostly sequential

instruction accesses. Also allow prefetching for eDMA and

DCU, assuming there are large blocks of graphic data

accessed.

Master n Access Protection MnAP = 3 for core data,

1 for core instructions,

eDMA and DCU

Assuming only the core will program flash, allow read and

write access (3) for the core data bus, but read access only

(1) for core instructions, eDMA and DCU.

Table 17-70. General flash memory setting recommendations for 64 MHz system clock

1

(continued)

Access Parameter

General Recommendations

Code flash (banks 0 and 2)

4 line buffers per port

Data flash (bank 1)

1 line buffer per port

Parameter

symbol

in register PFCR0

Comments

Parameter

symbolin register

PFCR1

Comments

Loading...

Loading...