9 OPAL-RT Technologies OP5600/OP5650 User Manual

OP5600 Series/OP5650 Simulator

Simulator Architecture

SIMULATOR ARCHITECTURE

configuration options

The OP5650 is available in a number of different configurations that make it easier to integrate into your

environment:

Product Configuration Description

OP5650-4 OP5650 RCP/HIL Artix 7 FPGA-based Real-Time Simulator - 4 cores (4U, Xeon E5, 4 Cores, 3.0 GHz,

10M, 16GB, 512GB SSD)

OP5650-8 OP5650 RCP/HIL Artix 7 FPGA-based Real-Time Simulator - 8 cores (4U, Xeon E5, 8 Cores, 3.2 GHz,

20M, 16GB, 512GB SSD)

OP5650-16 OP5650 RCP/HIL Artix 7 FPGA-based Real-Time Simulator - 16 cores (4U, Xeon E5, 2x8 Cores, 3.2 GHz,

2x20M, 2x16GB, 512GB SSD)

OP5650-32 OP5650 RCP/HIL Artix 7 FPGA-based Real-Time Simulator - 32 cores (4U, Xeon E5, 2x16 Cores, 2.3

GHz, 2x40M, 2x16GB, 512GB SSD)

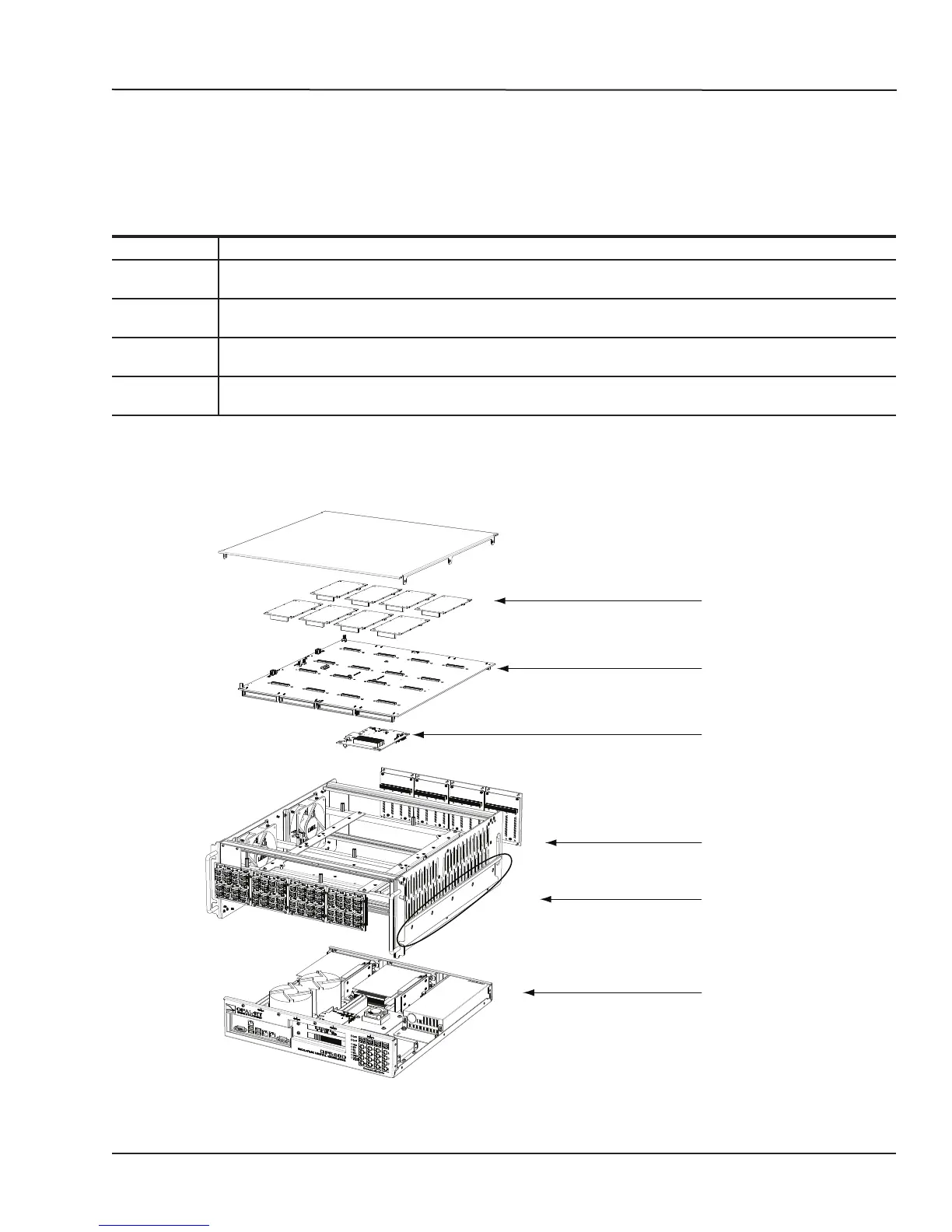

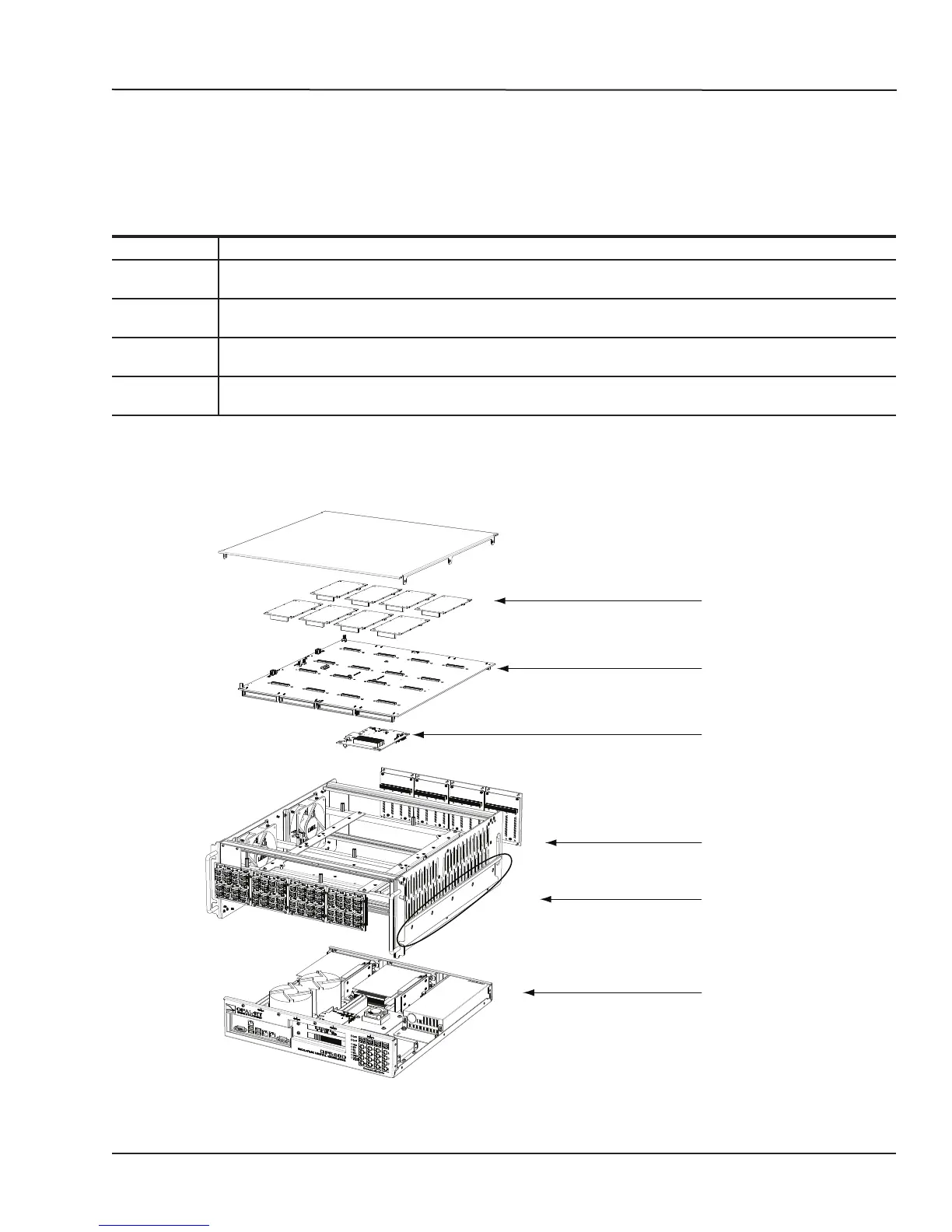

Simulator Architecture Example

The example shown is only to illustrate how the OP5650 is assembled. OPAL-RT strictly prohibits users

from opening the OP5650. Opening the unit will render the warranty null and void.

Signal conditioning

modules

Carrier board

OPAL-RT

Artix 7

FPGA board

Lower section

Target Computer

Upper section

optional rackmount rail

Figure 1: OP5650 with target computer

Loading...

Loading...