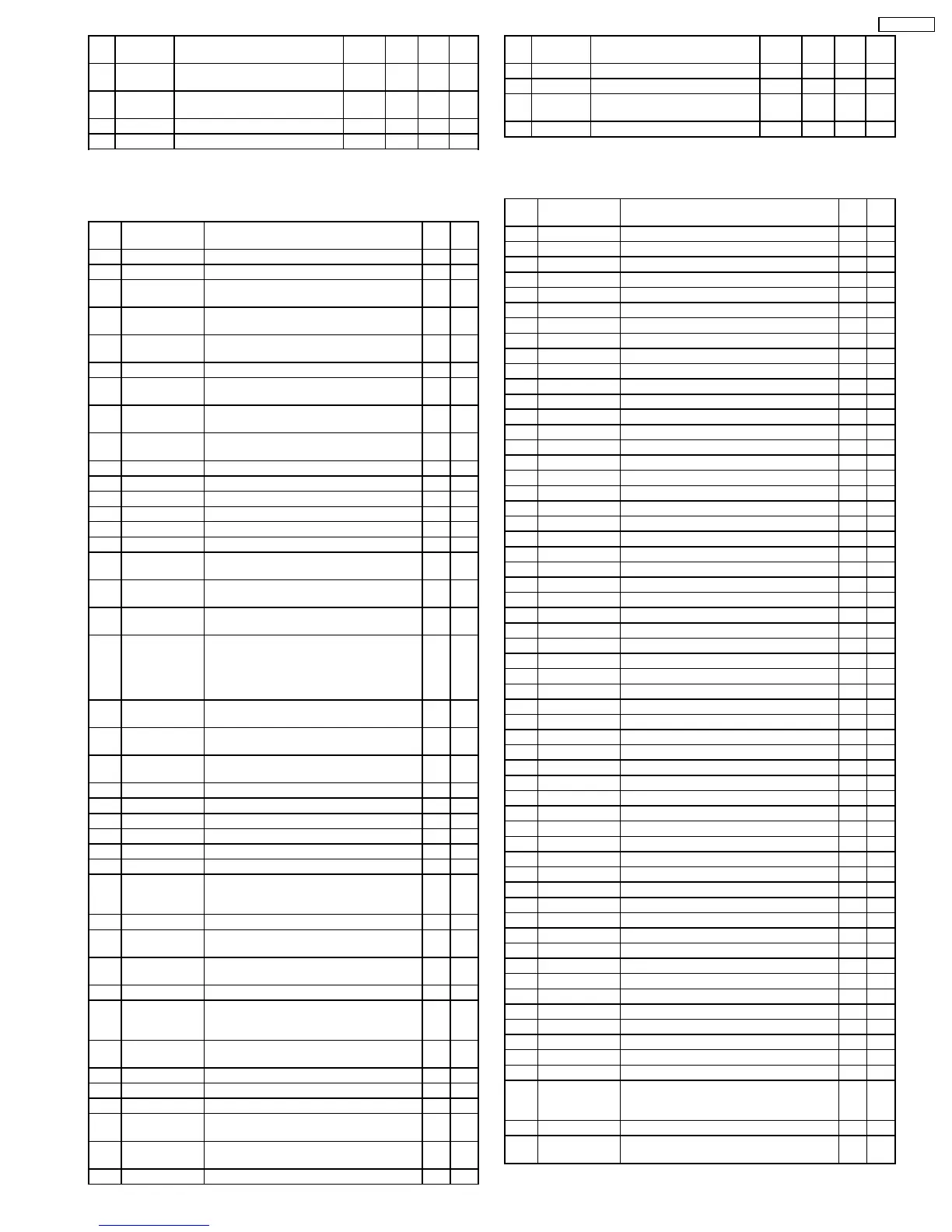

Pin

No.

Port Description I/O FM AM CD

93 SUB_RESE

T

Reset for display CPU O 5.1 5.1 5.1

94 DISPM_CO

NT

5V power control for

Display

O/I 0 0 0

95 NC Not connected O 0 0 0

96 NC Not connected O 0 0 0

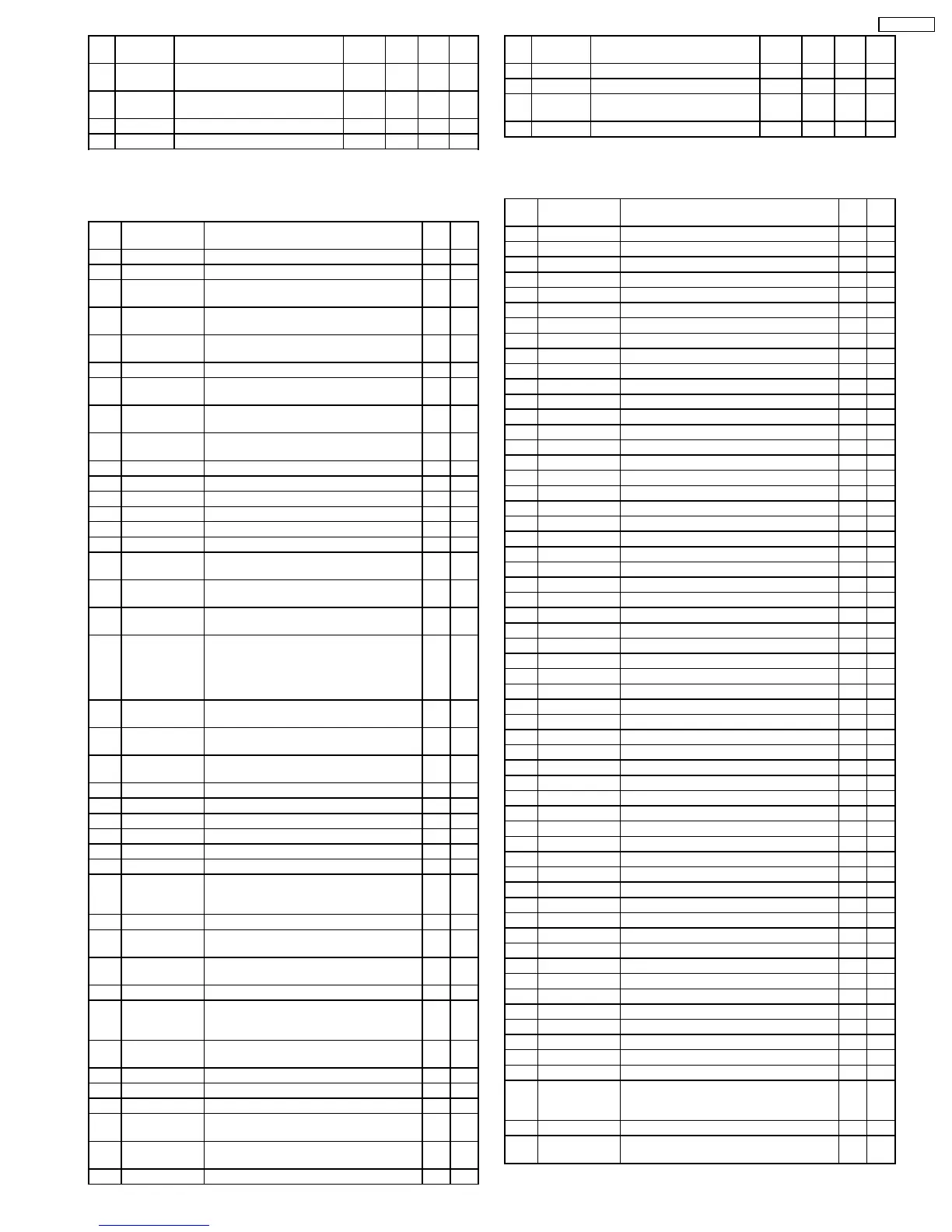

IC901:YEAM30879FL

Pin.

No.

Port Description I/O (V)

1 UART_SS4 GND I 0

2 UART_SS3 GND I 0

3 D_DIS Disable for Anode drive (Disable

for image signal)

O 4.7

4 PADJ2 Anode output pulse width

adjusting data 2(image data)

O 4.7

5 DCLK_SLV3 Slave D-CLK 3(Clock for image

data)

I 4.5

6 BUS_BYTE GND I 0

7 PMOD_CHG CPU rewrite mode/Single CPU mode

selection for Flash writer

I 0

8 IADJ Anode output current adjusting

data(Luminance control)

O 5

9 I_CLK Clock for anode output current

adjusting data

O 5

10 RESET Reset for Main CPU I 4.6

11 XOUT Ceramic oscillator clock(8Mhz) O 3.7

12 GND GND _ 0

13 XIN Ceramic oscillator clock(8Mhz) I 3.7

14 VCC5_0V Power supply _ 5

15 NMI Pulled up to H I 5

16 Y_SYNC Cathode scan data and cathode

latch control (Vertical sync)

O 4.7

17 ROTARY_A Volume-up detection from Rotary

encoder

I 0

18 ROTARY_B Volume-down detection from

Rotary encoder

I 0

19 X_SYNC Clock for Cathode scan ; or

Latch strobe for Anode output

pulse width adjusting data and

Anode output current adjusting

data

4.7

20 A_CLK_TA Anode output pulse width

adjusting clock

O 4.7

21 A_CLK_SCLK Anode pulse width adjustment

clock signal UART5

I 4.7

22 A_CLK Anode pulse width adjustment

clock signal UART5

O 4.7

23 S_DIS Disable for Cathode drive O 4.7

24 NC _ 0

25 OEL_RESET OEL RESET Output O 5

26 NC _ 0

27 SUB_SI CPU communication data output I 4.8

28 SUB_SO CPU communication data input O 4.8

29 PADJ1(TxD) Anode output pulse width

adjustment data signal 1 (image

data)UART1

O 4.7

30 _( R ) (D) NC O/I 0

31 DCLK_MST Master D-CLK (Clock for image

data)UART1

O 4.7

32 UART_SS4?BUS

Y?

GND O 0

33 OEL_OE OEL Outopttoinabl output O 0

34 PADJ0 Anode output pulse width

adjustment data signal 0 (image

data)UART0

O 4.7

35 DCLK_SLV0 Slave D-CLK 0 (Clock for image

data)

I 4.7

36 UART_SS0 GND I 0

37 RDY CPU RDY I 3.7

38 FLASH_RESET Reset for Flash memory O 3.7

39 HOLD EPM Program mode enable for Flash

writer

I 3.7

40 FLASH_WP Write protect/Accelaration from

Flash memory

O 3.7

41 FLASH_CE Chip enable for Flash memory O 0

Pin

No.

Port Description I/O FM AM CD

97 NC Not connected O 0 0 0

98 S_LED Security LED drive O 0 0 0

99 ANT_CONT Power control for antenna

motor

O 5.1 5.1 5.1

100 NC/EP_CS Not connected I 0 0 0

Pin.

No.

Port Description I/O (V)

42 FLASH_OE Output enable for Flash memory O 4.8

43 NC _ 4.8

44 FLASH_WE Write enable for Flash O 3.7

45 NC _ 3.7

46 FLASH_A22 A21 in Address bus O 4.5

47 FLASH_A21 A20 in Address bus O 4.5

48 FLASH_A20 A19 in Address bus O 4.5

49 FLASH_A19 A18 in Address bus O 4.5

50 FLASH_A18 A17 in Address bus O 4.5

51 FLASH_A17 A16 in Address bus O 4.5

52 FLASH_A16 A15 in Address bus O 4.7

53 FLASH_A15 A14 in Address bus O 4.7

54 FLASH_A14 A13 in Address bus O 4.7

55 FLASH_A13 A12 in Address bus O 4.7

56 FLASH_A12 A11 in Address bus O 4.7

57 FLASH_A11 A10 in Address bus O 4.7

58 FLASH_A10 A9 in Address bus O 4.7

59 FLASH_A9 A8 in Address bus O 4.7

60 VDD 3.3V +3.3v Power supply _ 3.8

61 FLASH_A8 A7 in Address bus O 4.7

62 GND GND _ 0

63 FLASH_A7 A6 in Address bus O 4.7

64 FLASH_A6 A5 in Address bus O 4.7

65 FLASH_A5 A4 in Address bus O 4.7

66 FLASH_A4 A3 in Address bus O 4.7

67 FLASH_A3 A2 in Address bus O 4.7

68 FLASH_A2 A1 in Address bus O 4.7

69 FLASH_A1 A0 in Address bus O 4.7

70 FLASH_RY/BY Pulled up to H I 4.7

71 FLASH_D15 DQ15 in Data bus I/O 4.7

72 FLASH_D14 DQ14 in Data bus I/O 4.7

73 FLASH_D13 DQ13 in Data bus I/O 4.7

74 FLASH_D12 DQ12 in Data bus I/O 4.7

75 FLASH_D11 DQ11 in Data bus I/O 4.7

76 FLASH_D10 DQ10 in Data bus I/O 4.7

77 FLASH_D9 DQ9 in Data bus I/O 4.7

78 FLASH_D8 DQ8 in Data bus I/O 4.7

79 FLASH_D7 DQ7 in Data bus I/O 4.7

80 FLASH_D6 DQ6 in Data bus I/O 4.7

81 FLASH_D5 DQ5 in Data bus I/O 4.7

82 FLASH_D4 DQ4 in Data bus I/O 4.7

83 FLASH_D3 DQ3 in Data bus I/O 4.7

84 FLASH_D2 DQ2 in Data bus I/O 4.7

85 FLASH_D1 DQ1 in Data bus I/O 4.7

86 FLASH_D0 DQ0 in Data bus I/O 4.7

87 KEY_RET4 Keyreturn4 I 0

88 KEY_RET3 Keyreturn3 I 0

89 KEY_RET2 Keyreturn2 I 0

90 KEY_RET1 Keyreturn1 I 0

91 KS3 Key scan 3 I/O 4.7

92 KS2 Key scan 2 I/O 4.7

93 KS1 Key scan 1 I/O 4.7

94 AD_AVSS A/D converter grand potential _ 0

95 TH_DETECT Temperature detection input I 2

96 AD_VREF +5v Power supply _ 5

97 AD_AVCC +5v Power supply _ 5

98 PADJ3 Anode output pulse width

adjustment data signal 3 (image

data)UART4

O 4.7

99 NC _ 0

100 DCLK_SLV4 Slave D-CLK 4 (Clock for image

data)

I 4.7

11.2. Display Block

13

CQ-C8305U

Loading...

Loading...