Triggers

R&S

®

RTP

254User Manual 1337.9952.02 ─ 12

Figure 6-5: High-speed serial pattern trigger dialog

1 = Basic settings

2 = Serial standard

3 = UI offset

4 = Nom. bit rate

5 = Pattern type

6 = Pattern type specific settings

Basic trigger settings

In the basic settings you need to define if the clock data recovery is used for extracting

a clock signal from the signal (enabled CDR), or if a dedicated clock signal is provided

by an additional channel (disabled CDR).

Digital high-speed serial data streams, use typically an embedded clock. No additional

accompanying clock signal such as for parallel buses (e.g. DDR memory interface

DDR3/ DDR4) are required.

With enabled CDR the timing information embedded in the data, signal is extraced and

a clock signal that can be further processed by the trigger system is generated. The

internally generated CDR clock signal is used to sample the original data signal and

decode the sequence of transmitted bits.

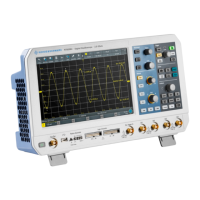

The following example displays the trigger position for a single bit pattern using the

hardware CDR setup:

High-speed serial pattern trigger (Option R&S RTP-K140/K141)

Loading...

Loading...