2-2 0

Chapter 2: BI OS set up

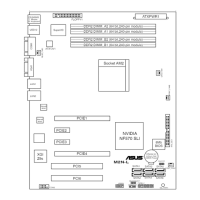

North Bridge chipset Conguration

Memory Conguration

Memclock Mode [Auto]

MCT Timing Mode [Auto]

Enable Clock to ALL DIMMs [Disabled]

MemCLK Tristate C3/ATLVID [Disabled]

Memory Hole Remapping [Enabled]

Power Down Control [Auto]

NorthBridge Configuration

2.4.2 Chipset

The Chipset menu allows you to change the advanced chipset settings.

Select an item then press <Enter> to display the sub-menu.

Advanced Chipset Settings

WARNING: Setting wrong values in below sections

may cause the system to malfunction.

NorthBridge Conguration

Southbridge

Hyper Transport Conguration

MTRR Mapping [Continuous]

This option determines the method used for programming CPU MTRRs when

4GB or more of memory is present. Discrete leaves the PCI hole below the

4GB boundary undescribed. Continuous explicitly describes the PCI hole as

non-caheable. Conguration options: [Continuous] [Discrete]

Runtime Legacy PSB [Disabled]

Enables or disables the generation of Power State Block for use of

PowerNow(tm) driver in a single core system.

Conguration options: [Disabled] [Enabled]

ACPI 2.0 Objects [Enabled]

Enables or disables the generation of ACPI_PPC, _PSS, and _PCT objects.

Conguration options: [Disabled] [Enabled]

Loading...

Loading...