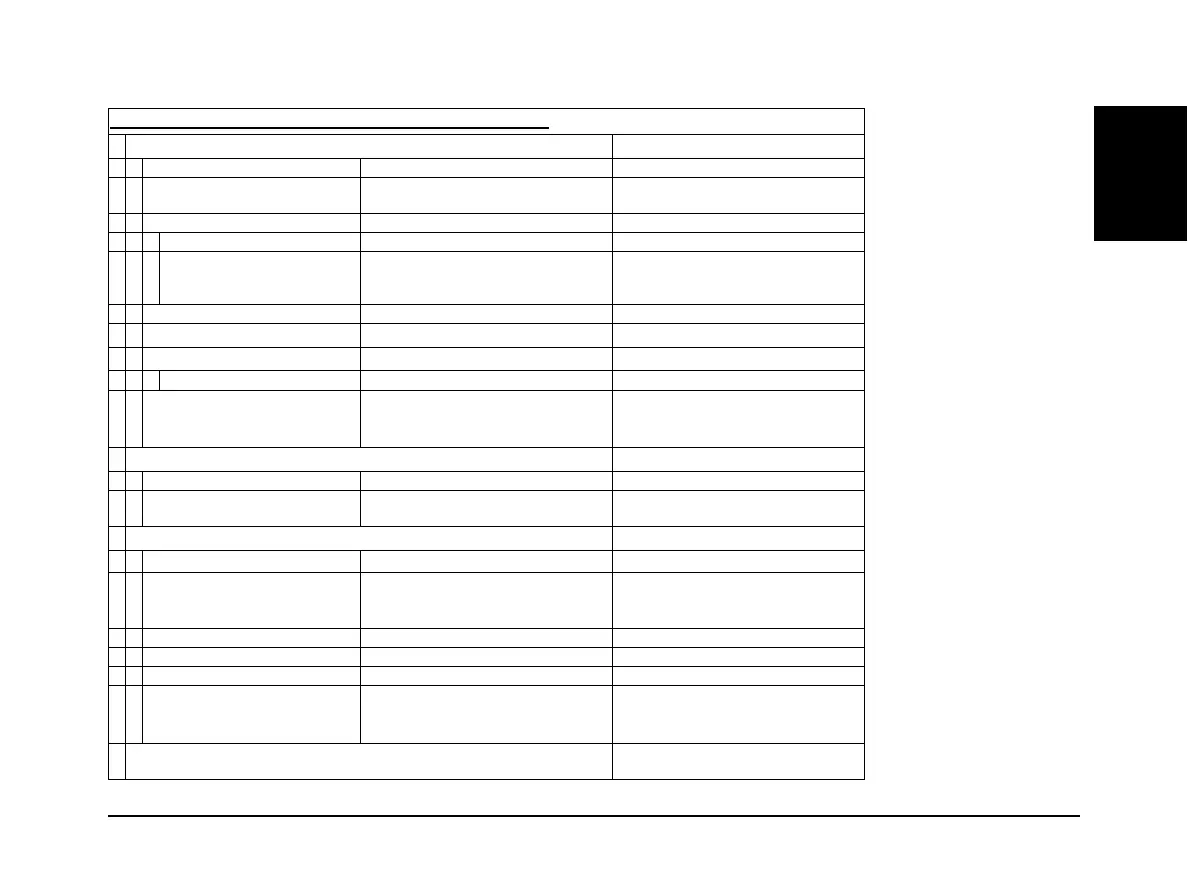

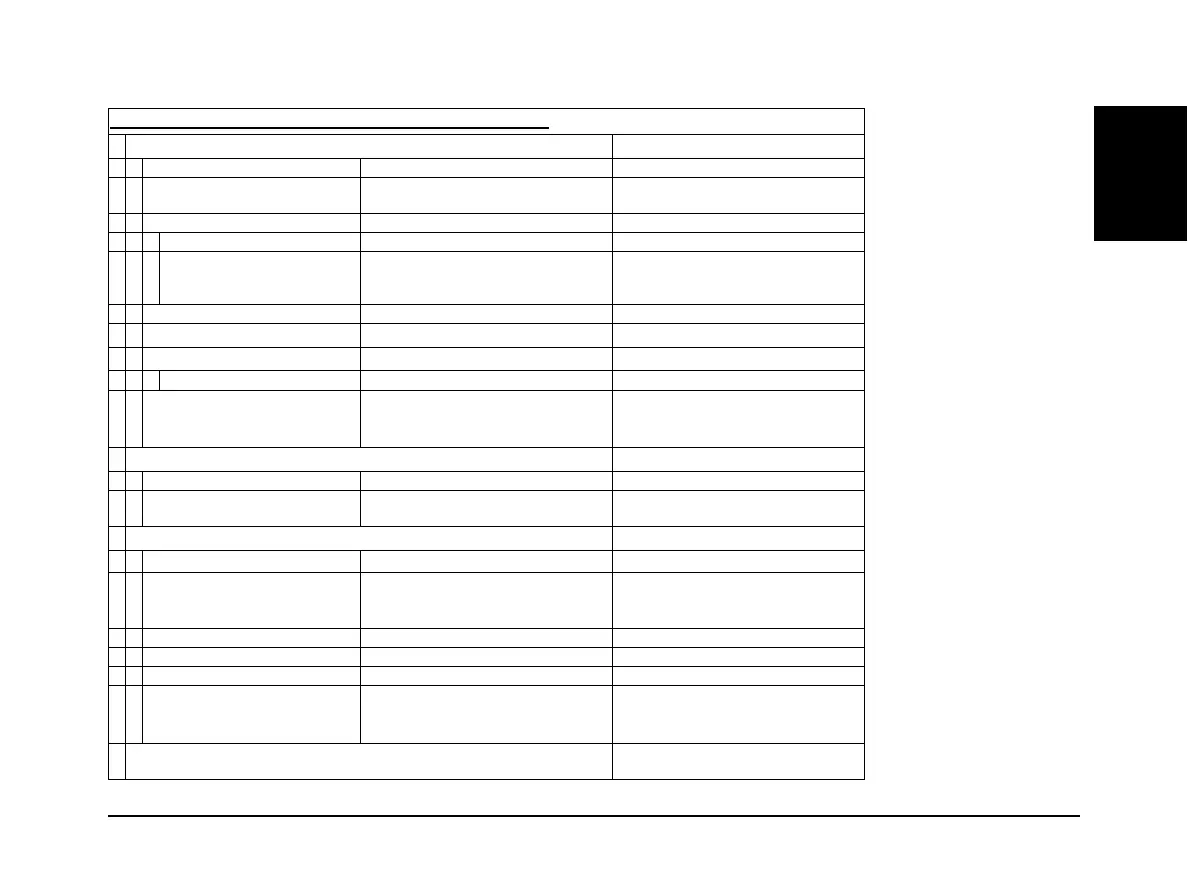

Characteristic Specifications Supplemental Information

APx DSIO Module for B Series: Specifications 59

DSIO

Clock Jitter (Advanced Master Clock required)

Jitter Measurement

Range 0 to 650 ns

Detection Peak, RMS, or Average “Average” detection is recommended

for jitter response measurements.

Bandwidth

Low Limit 50 Hz or 700 Hz

High Limit Variable from 1 kHz to 150 kHz in

0.1 kHz steps, Butterworth or Elliptic

response

Accuracy (1 kHz) ±(1% + 300 ps) “Average” detection

Flatness

1

±0.2 dB, 100 Hz to 100 kHz

Residual Jitter

1

700 Hz to 100 kHz BW 600 ps

Jitter Spectrum

1

Spurious products are typically

–40 dBc (below jitter signal) or

–60 dBUI, whichever is larger.

3

Induced Jitter

Waveforms Sine, Square, Noise

Signals Affected Master Clk, Bit Clk, Frame Clock and

Data

Sine Wave Jitter

Frequency Range (F

J

) 2 Hz to 200 kHz

Amplitude Range 0 to 1591 ns for F

J

20 kHz, derating

linearly with frequency to 159.1 ns at

200 kHz

Equivalent to 0 to 9.775 UI at 48 kHz

sample rate, derating to 0.9775 UI.

3

Amplitude Resolution 100 ps

Accuracy (1 kHz) ±0.01%

Flatness ±0.01%

Jitter Spectrum

1

Spurious products are typically

–40 dBc (below jitter signal) or

–60 dBUI, whichever is larger.

3

Square Wave and Noise Waveform Jitter Jitter amplitude limited to 40 ns

maximum.

Loading...

Loading...