14

14

DCD-SA100

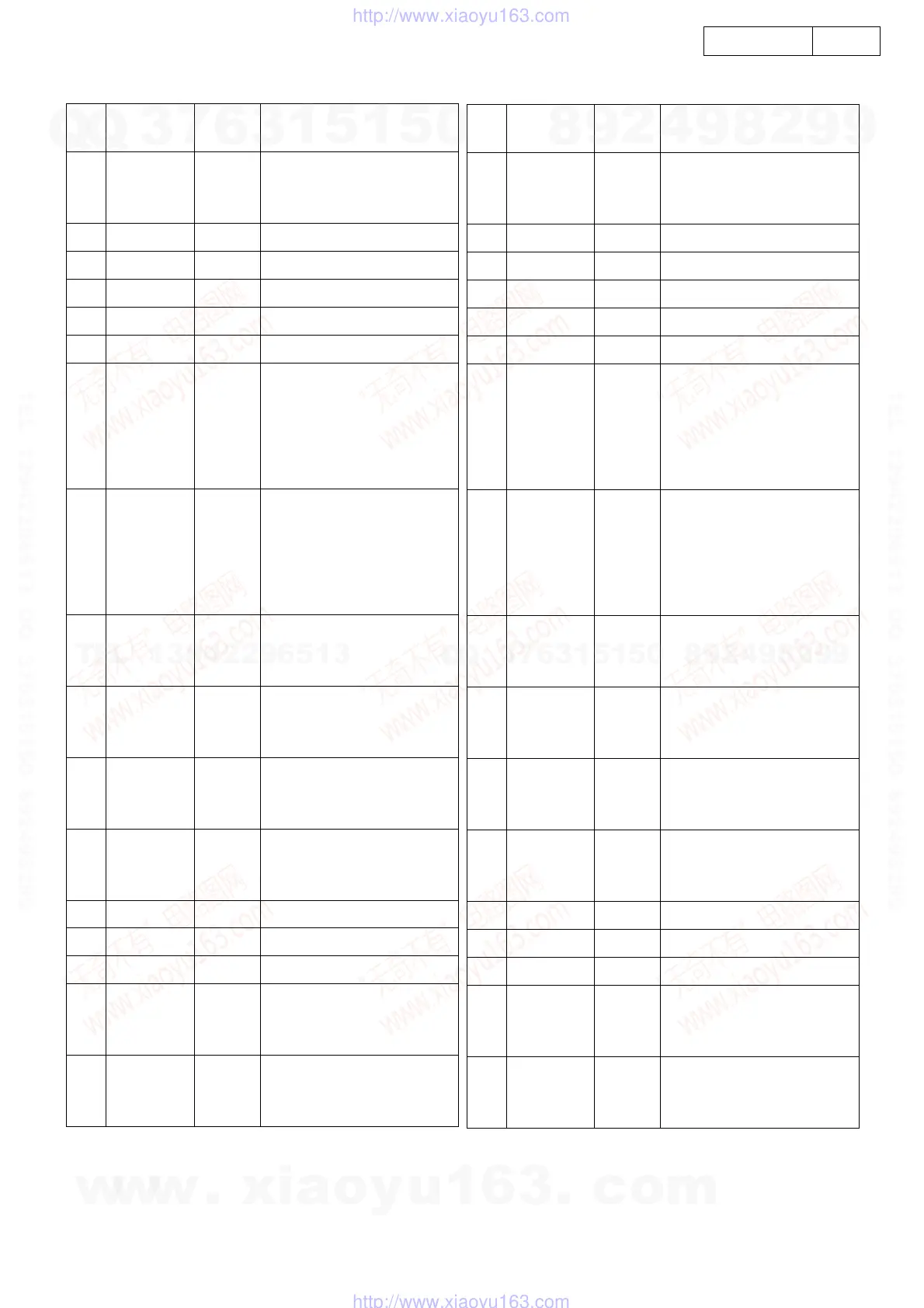

(7) Test mode detailed table

Table 1: servo adjustment value display mode details

XX Contents

Contents

suppleme

nt

Contentsexplanation

31 RFPFEOffset layer0 PIofCXD1881ARAnoffsetvalueand

FEAnoffsetvalueisdisplayed.

Pi offset is shown in higher rank

1Byte.

FEoffsetisshowninlowrank1Byte.

32 RFP TE Bal

Gain

layer0 TEbalancegainvalueofCXD1881AR

isdisplayed.

33 RFP TEOutput

Gain

layer0 TEoutputgainvalueofCXD1881ARis

displayed.

34 RFPTEOffset layer0 TE offset value of CXD1881AR is

displayed.

35 DSPTEOffset layer0 TE offset value inside CXD1885Q is

displayed.

36 FcsBias layer0 The focus bias value inside

CXD1885Qisdisplayed.

37 FcsAGC layer0 Theinsidefocusgain(setting0x2000

to 1) value of CXD1885Q is

displayed.。

Therefore,0x1FF2andinthecaseof

0x2012,itisasfollows.

0x1FF2(8178) / 0x2000(8192) =

0.998291015625(fold)

0x2012(8210) / 0x2000(8192) =

1.002197265625(fold)

Notes:Theinsideof()isadecimal

systemequivalent.

38 TrkAGC layer0 The inside tracking gain (setting

0x2000 to 1) value of CXD1885Q is

displayed.。

Therefore,0x1FF2andinthecaseof

0x2012,itisasfollows.

0x1FF2(8178) / 0x2000(8192) =

0.998291015625(fold)

0x2012(8210) / 0x2000(8192) =

1.002197265625(fold)

Notes:Theinsideof()isadecimal

systemequivalent

39 PiOffset layer0 It is the parameter calculated inside

CXD1885Q.

Thevaluedisplayedonasetservesas

the number of complement of 2 of

2Bytes(es)doubled256.

Avoltagevalueis6.25mVperbit.

40 FEOffset layer0 It is the parameter calculated inside

CXD1885Q.

Thevaluedisplayedonasetservesas

the number of complement of 2 of

2Bytes(es)doubled256.

Avoltagevalueis6.25mVperbit.

41 SEOffset layer0 It is the parameter calculated inside

CXD1885Q.

Thevaluedisplayedonasetservesas

the number of complement of 2 of

2Bytes(es)doubled256.

Avoltagevalueis6.25mVperbit.

42 RFPFEOffset layer1 PIofCXD1881ARAnoffsetvalueand

FEAnoffsetvalueisdisplayed.

Pi offset is shown in higher rank

1Byte.

FEoffsetisshowninlowrank1Byte.

43 RFP TE Bal

Gain

layer1 TEbalancegainvalueofCXD1881AR

isdisplayed.

44 RFP TEOutput

Gain

layer1 TEoutputgainvalueofCXD1881ARis

displayed.

45 RFPTEOffset layer1 TE offset value of CXD1881AR is

displayed.

46 DSPTEOffset layer1 It is the parameter calculated inside

CXD1885Q.

Thevaluedisplayedonasetservesas

the number of complement of 2 of

2Bytes(es)doubled256.

Avoltagevalueis6.25mVperbit.

47 FcsBias layer1 It is the parameter calculated inside

CXD1885Q.

Thevaluedisplayedonasetservesas

the number of complement of 2 of

2Bytes(es)doubled256.

Avoltagevalueis6.25mVperbit.

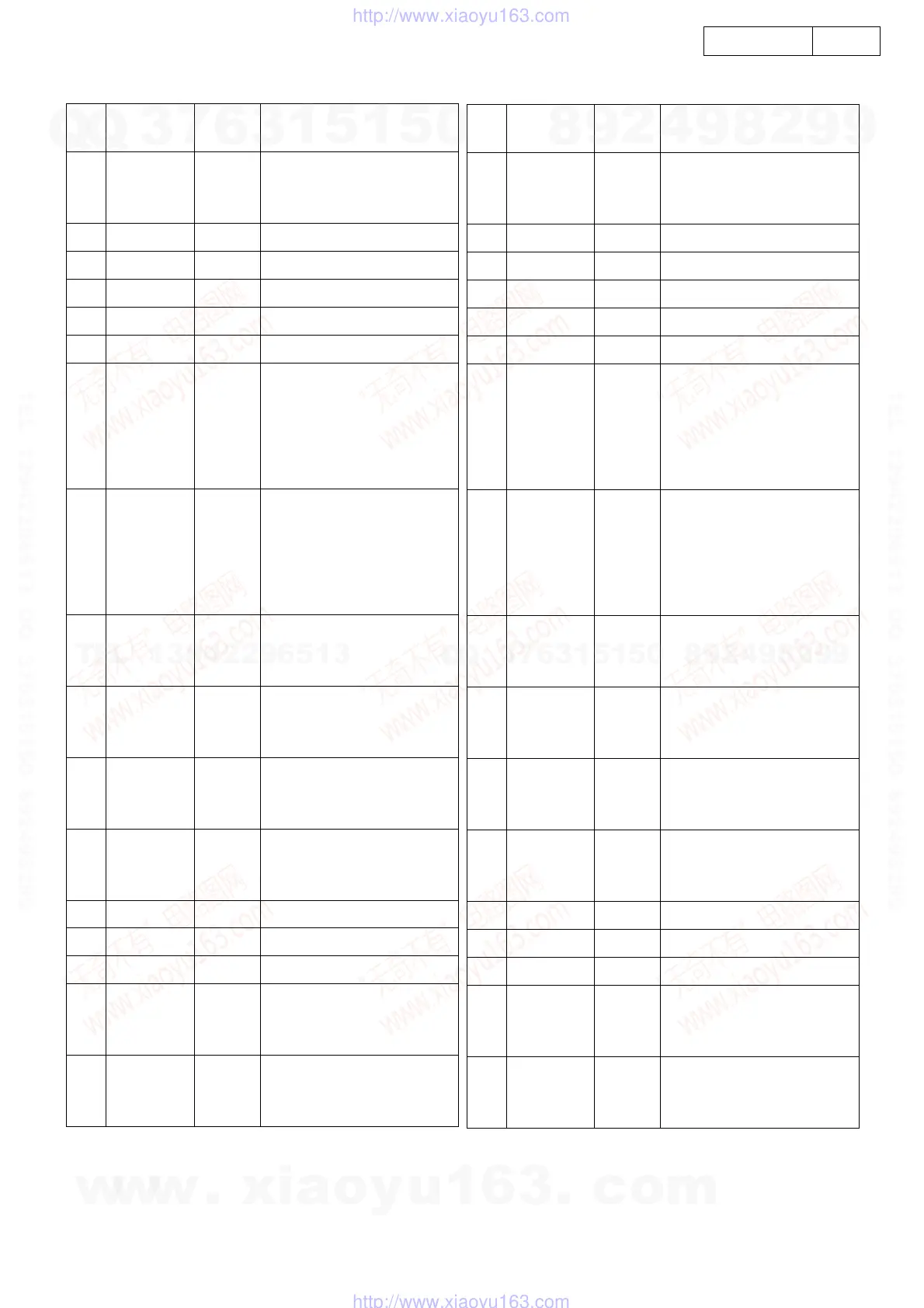

(7) テストモード詳細一覧表

表 1サーボ調整値表示モード詳細

XX 内容 内容補足 内容説明

31 RFPFEOffset レイヤ 0 CXD1881AR の PIオフセット値と FE

オフセット値を表示。

上位 1Byte に Pi オフセットを示す。

下位 1Byte に FEオフセットを示す。

32 RFP TE Bal

Gain

レイヤ 0 CXD1881ARのTEバランスゲイン値を

表示す。

33 RFPTEOutput

Gain

レイヤ 0 CXD1881ARのTE出力ゲイン値を表示

す。

34 RFPTEOffset レイヤ 0 CXD1881AR の TEオフセット値を表

示。

35 DSPTEOffset レイヤ 0 CXD1885Q 内部の TE オフセット値を

表示。

36 FcsBias レイヤ 0 CXD1885Q 内部のフォーカスバイア

ス値を表示。

37 FcsAGC レイヤ 0 CXD1885Q 内部フォーカスゲイン

(0x2000 を 1 として ) 値を表示。

0x1FF2 や 0x2012 の場合、以下のよ

うになる。

0x1FF2(8178) / 0x2000(8192) =

0.998291015625( 倍 )

0x2012(8210) / 0x2000(8192) =

1.002197265625( 倍 )

注 :() 内は 10 進換算値

38 TrkAGC レイヤ 0 CXD1885Q内部トラッキングゲイン(0

x2000を1として)値を表示。

0x1FF2 や 0x2012 の場合、以下のよ

うになる。

0x1FF2(8178) / 0x2000(8192) =

0.998291015625( 倍 )

0x2012(8210) / 0x2000(8192) =

1.002197265625( 倍 )

注 :() 内は 10 進換算値

39 PiOffset レイヤ 0 CXD1885Q 内部で計算されるパラ

メータ。

セットに表示される値は、256 倍され

た 2Bytes の 2 の補数となる。

電圧値は 1bit あたり 6.25mV。

40 FEOffset レイヤ 0 CXD1885Q 内部で計算されるパラ

メータ。

セットに表示される値は、256 倍され

た 2Bytes の 2 の補数となる。

電圧値は 1bit あたり 6.25mV。

41 SEOffset レイヤ 0 CXD1885Q 内部で計算されるパラ

メータ。

セットに表示される値は、256 倍され

た 2Bytes の 2 の補数となる。

電圧値は 1bit あたり 6.25mV。

42 RFPFEOffset レイヤ 1 CXD1881AR の PIオフセット値と FE

オフセット値を表示。

上位 1Byte に Pi オフセットを示す。

下位 1Byte に FEオフセットを示す。

43 RFP TE Bal

Gain

レイヤ 1 CXD1881ARのTEバランスゲイン値を

表示。

44 RFPTEOutput

Gain

レイヤ 1 CXD1881AR の TE出力ゲイン値を表

示。

45 RFPTEOffset レイヤ 1 CXD1881AR の TEオフセット値を表

示。

46 DSPTEOffset レイヤ1 CXD1885Q 内部で計算されるパラ

メータ。

セットに表示される値は、256 倍され

た 2Bytes の 2 の補数となる。

電圧値は 1bit あたり 6.25mV。

47 FcsBias レイヤ 1 CXD1885Q 内部で計算されるパラ

メータ。

セットに表示される値は、256 倍され

た 2Bytes の 2 の補数となる。

電圧値は 1bit あたり 6.25mV。

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...