Basys2™ FPGA Board Reference Manual

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

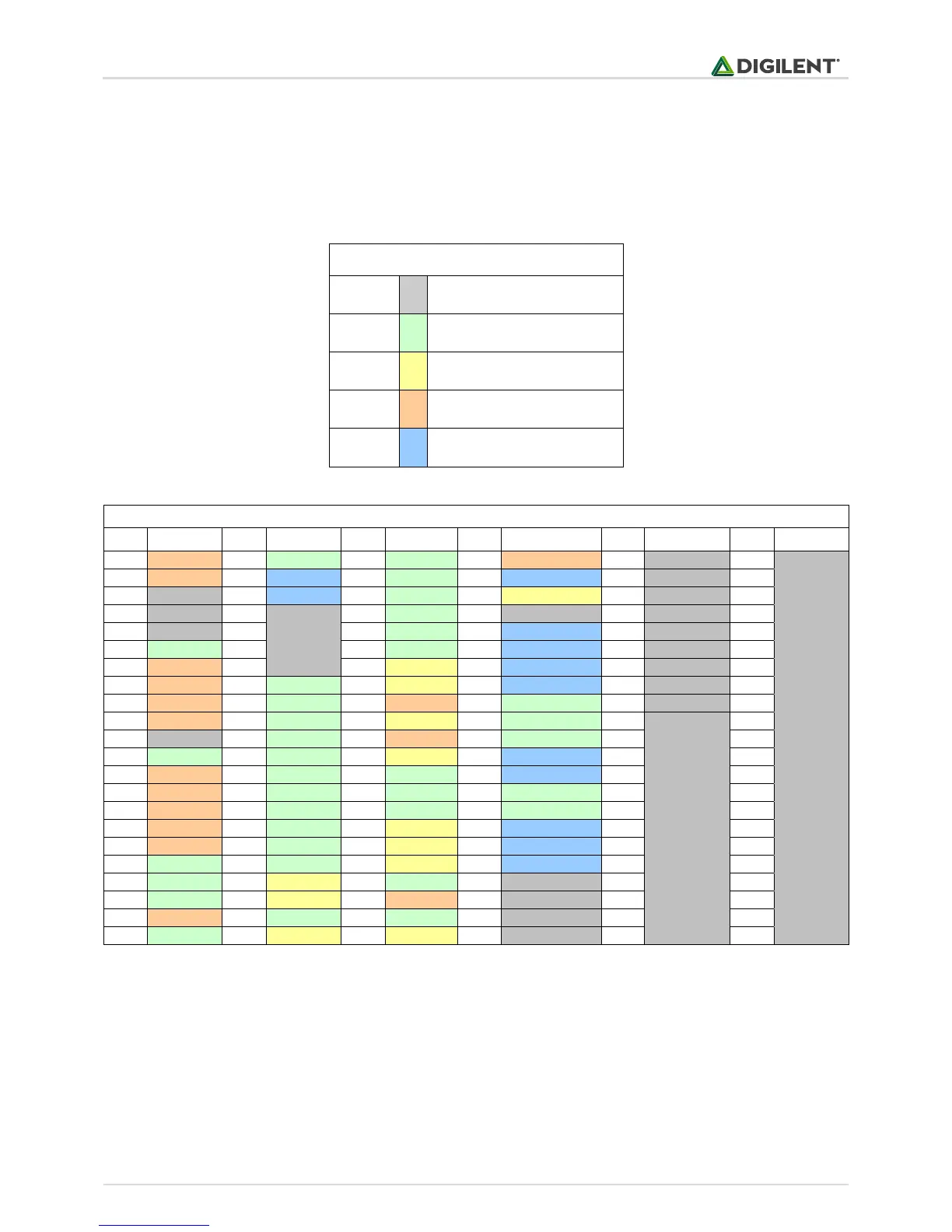

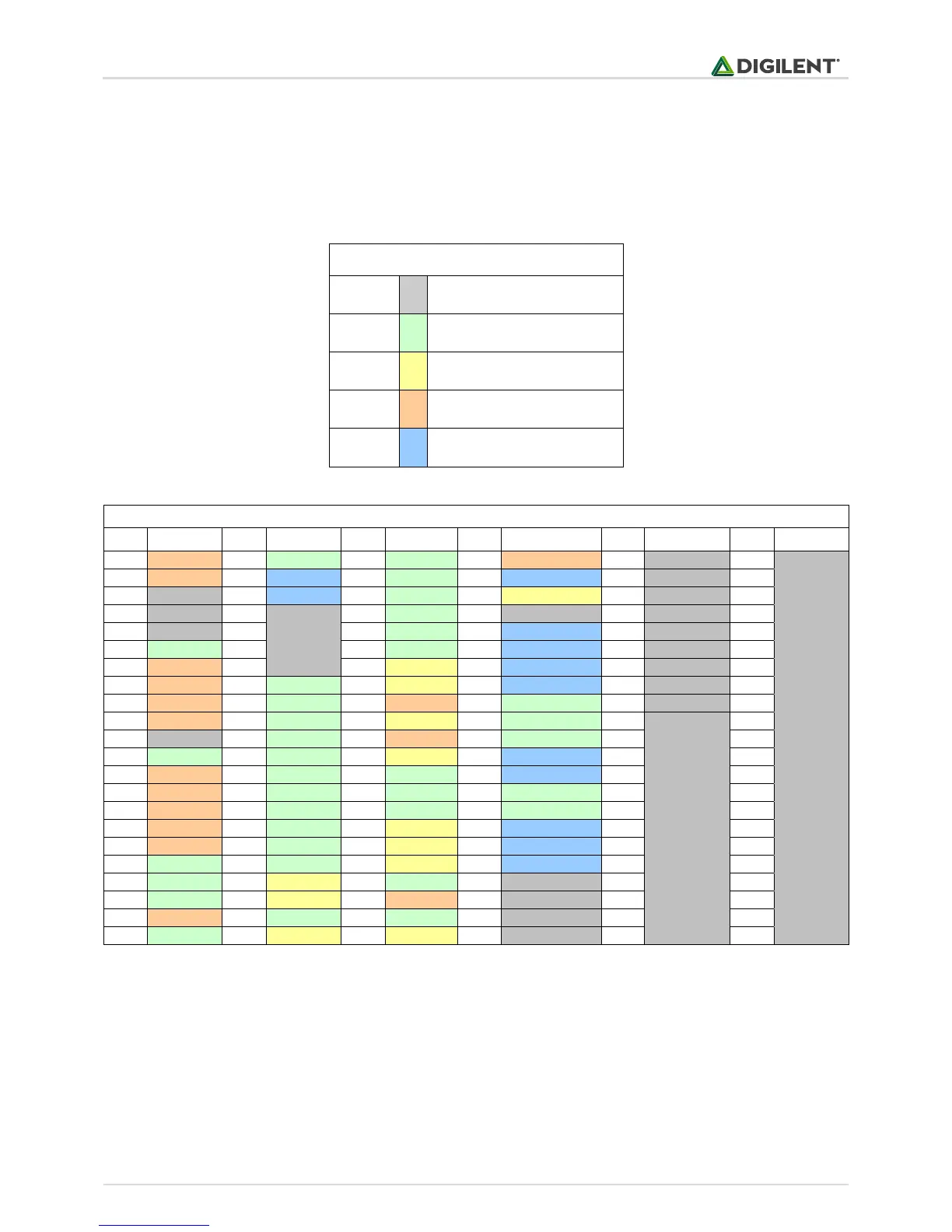

8 FPGA Pin Definitions

The table below shows all pin definitions for the Spartan-3E on the Basys 2 board. Pins in grey boxes are not

available to the user.

FPGA pin definition table color key

Basys 2 Spartan-3E pin definitions

9 Built-In Self Test

The Basys 2 board comes preloaded with a simple self test/demonstration project stored in its ROM. The demo

project (available at the website) shows how the Xilinx CAD tools connect FPGA signals to Basys 2 circuits. Since the

project is stored in ROM, it can also be used to check board functions. To run the demo, set the ROM/USB jumper

(JP3) to ROM and apply power to the board; the seven-segment display will show counting digits, the switches will

turn on individual LEDs, the buttons will turn off individual digits on the seven segment display, and a test pattern

is driven on the VGA port.

Loading...

Loading...