HMCS44C,HMCS44CL--------------------------------------------------------

• Designation

of

ROM Address and ROM Code

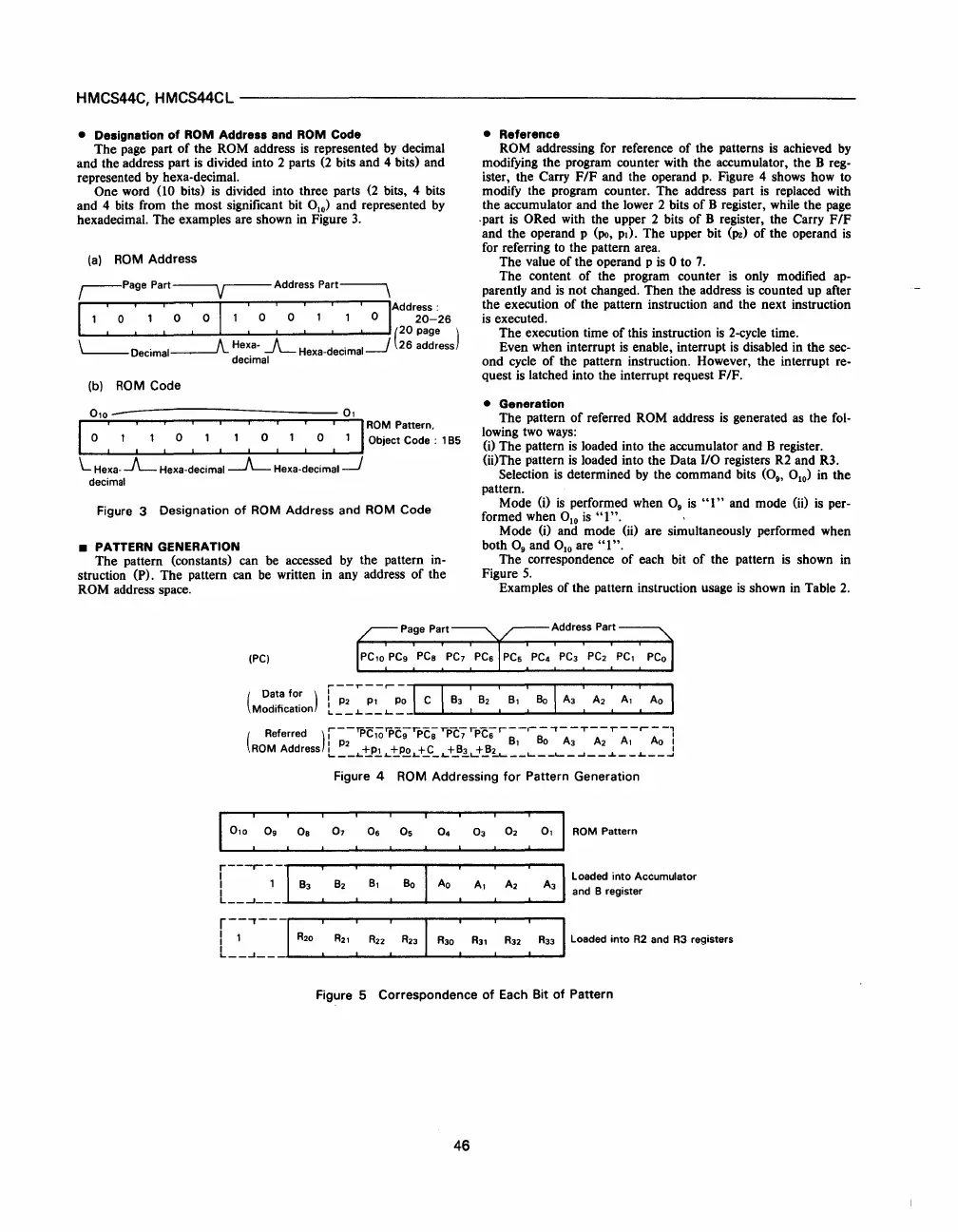

The page part

of

the ROM address

is

represented

by

decimal

and the address part

is

divided into 2 parts

(2

bits and 4 bits) and

represented

by

hexa-decimal.

One word (IO bits)

is

divided into three parts

(2

bits, 4 bits

and 4

bits

from the most significant bit 0

10

)

and represented

by

hexadecimal. The examples are shown

in

Figure

3.

(a)

ROM

Address

(b)

ROM

Code

010-

01

I

0:

: :

0:

: :

0:

: 0 : 1

I~~:c~~:e;:.:

1B5

\....

Hexa·

~

Hexa-decimal

~

Hexa-decimal

~

decimal

Figure 3 Designation

of

ROM Address and ROM Code

• PATTERN GENERATION

The pattern (constants) can be accessed

by

the pattern in-

struction (P). The pattern can be written

in

any address

of

the

ROM address space.

• Reference

ROM

addressing for reference

of

the patterns

is

achieved

by

modifying the program counter with the accumulator, the B reg-

ister, the Carry FIF and the operand

p.

Figure 4 shows how to

modify the program counter. The address part

is

replaced with

the accumulator and the lower 2 bits

of

B register, while the page

·part

is

ORed with the upper 2 bits

of

B register, the Carry FIF

and the operand p (po, pI). The upper bit

(P2)

of

the operand

is

for referring

to

the pattern area.

The value

of

the operand p

is

0 to

7.

The content

of

the program counter

is

only modified ap-

parently and

is

not changed. Then the address

is

counted up after

the execution of the pattern instruction and the next instruction

is

executed.

The execution time

of

this instruction

is

2-cycle time.

Even when interrupt

is

enable, interrupt

is

disabled

in

the sec-

ond

cycle

of

the pattern instruction. However, the interrupt re-

quest

is

latched into the interrupt request

FIF.

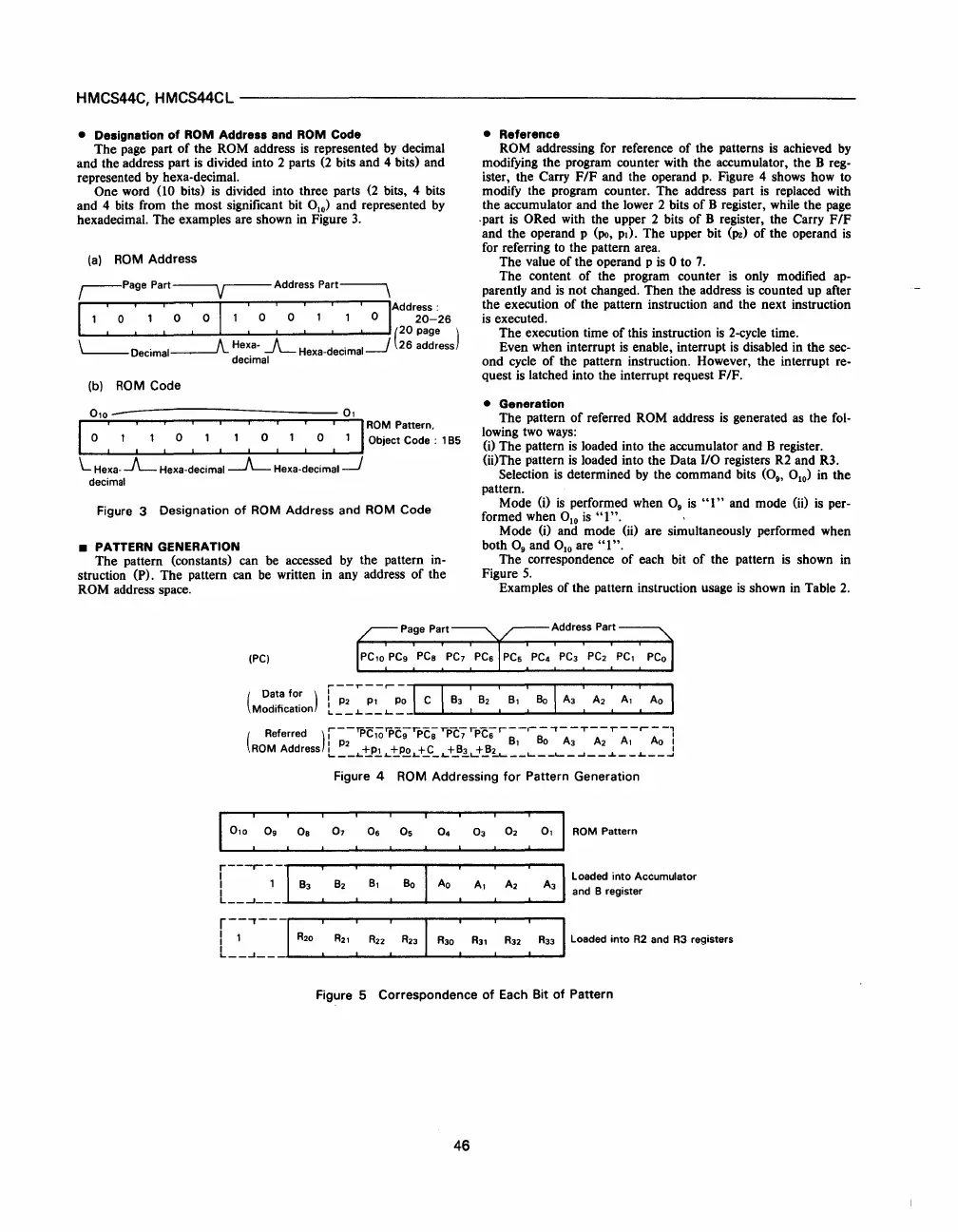

• Generation

The pattern

of

referred

ROM

address

is

generated

as

the

fol-

lowing

two

ways:

(i) The pattern

is

loaded into the accumulator and B register.

(ii)The pattern

is

loaded into the Data I/O registers

R2

and

R3.

Selection

is

determined

by

the command bits

(0

9

,

0

10

)

in

the

pattern.

Mode

(j)

is

performed when 0

9

is

"1"

and mode

(ij)

is

per-

formed when

010

is

"1".

Mode

(i)

and mode

(ij)

are simultaneously performed when

both 0

9

and

010

are

"1"

.

The correspondence of each bit

of

the pattern

is

shown in

Figure

5.

Examples of the pattern instruction usage

is

shown

in

Table

2.

Figure 4 ROM Addressing

for

Pattern Generation

I 0

1

0:

Os

:

08

:

07

:

06

:

05

:

04

: OJ :

02

: 01 I

ROM

Pattern

r---r

I

I

I

L

__

...J

I

B3

:

B2

:

Bl

:

Bo

I

Ao

:

Al

:

A2

:

A31

~~:d;dr~~~:t;CCumulator

I

R20

:

R21

: R22: R231 R30:

R31

:

R32

: R331 Loaded into

R2

and

R3

registers

Figure 5 Correspondence

of

Each Bit

of

Pattern

46

Loading...

Loading...