HMCS45C(H044820)----

H M

CS45CL(

H

044828)

The HMCS45C

is

the CMOS 4-bit single chip microcomputer

which contains ROM, RAM, I/O and Timer/Event Counter on

single chip. The

HMCS45C

is

designed to perform efficient con-

troller function as

well

as arithmetic function for both binary and

BCD data. The

CMOS technology

of

the HMCS45C provides the

flexibility

of

microcomputers for battery powered and battery

back-up applications.

• FEATURES

•

4-bit Architecture

• 2,048 Words

of

Program

ROM

(10 bits/Word)

128 Words

of

Pattern

ROM

(10 bits/Word)

• 160 Digits

of

Data

RAM (4 bits/Digiti

•

44

I/O

Lines

and 2 External Interrupt

Lines

• Timer/Event Counter

• Instruction Cycle

Time: HMCS45C;

10

p's

HMCS45CL;

20

p.s

• All Instructions except

One

Instruction; Single Word

and

Single Cycle

•

BCD

Arithmetic Instructions

•

Pattern Generation Instruction

- Table Look Up Capability -

• Powerful Interrupt Function

3

Interrupt Sources

~

2 External Interrupt Lines

L Timer/Event Counter

Multiple Interrupt

Capability

• Bit Manipulation Instructions

for

Both

RAM

and I/O

• Option

of

I/O Configuration Selectable

on

Each

Pin; Pull

Up

MOS

or

CMOS

or

Open

Drain

• Built-in Oscillator

• Built-in Power-on Reset Circuit (HMCS45C only)

•

Low Operating Power Dissipation;

2mW

typo

• Stand-by Mode

(Halt

Mode);

50

p.

W

max.

•

CMOS

Technology

• Single Power Supply: HMCS45C;

5V±

1

0%

HMCS45CL; 2.5V to 5.5V

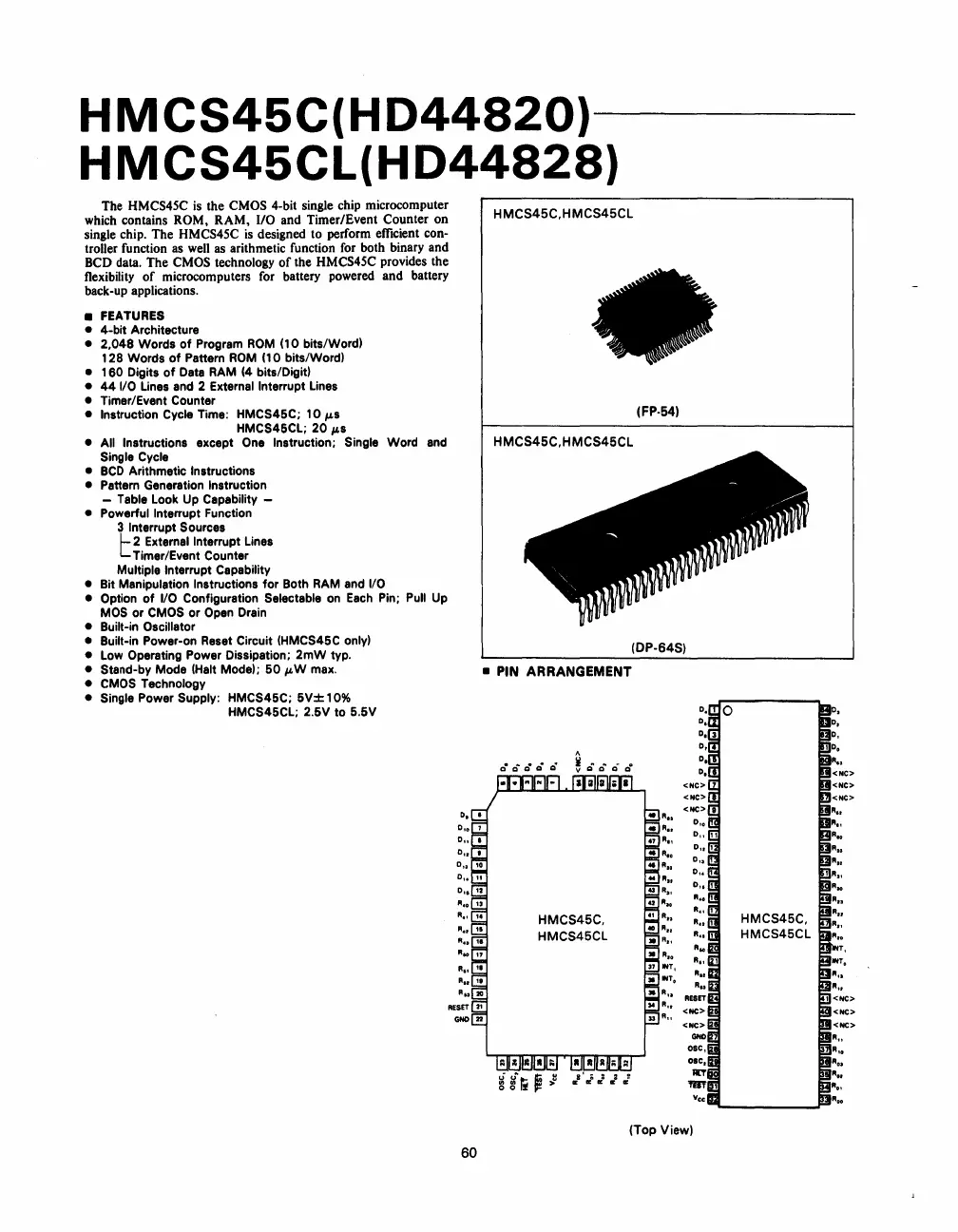

HMCS45C,HMCS45CL

(FP-54)

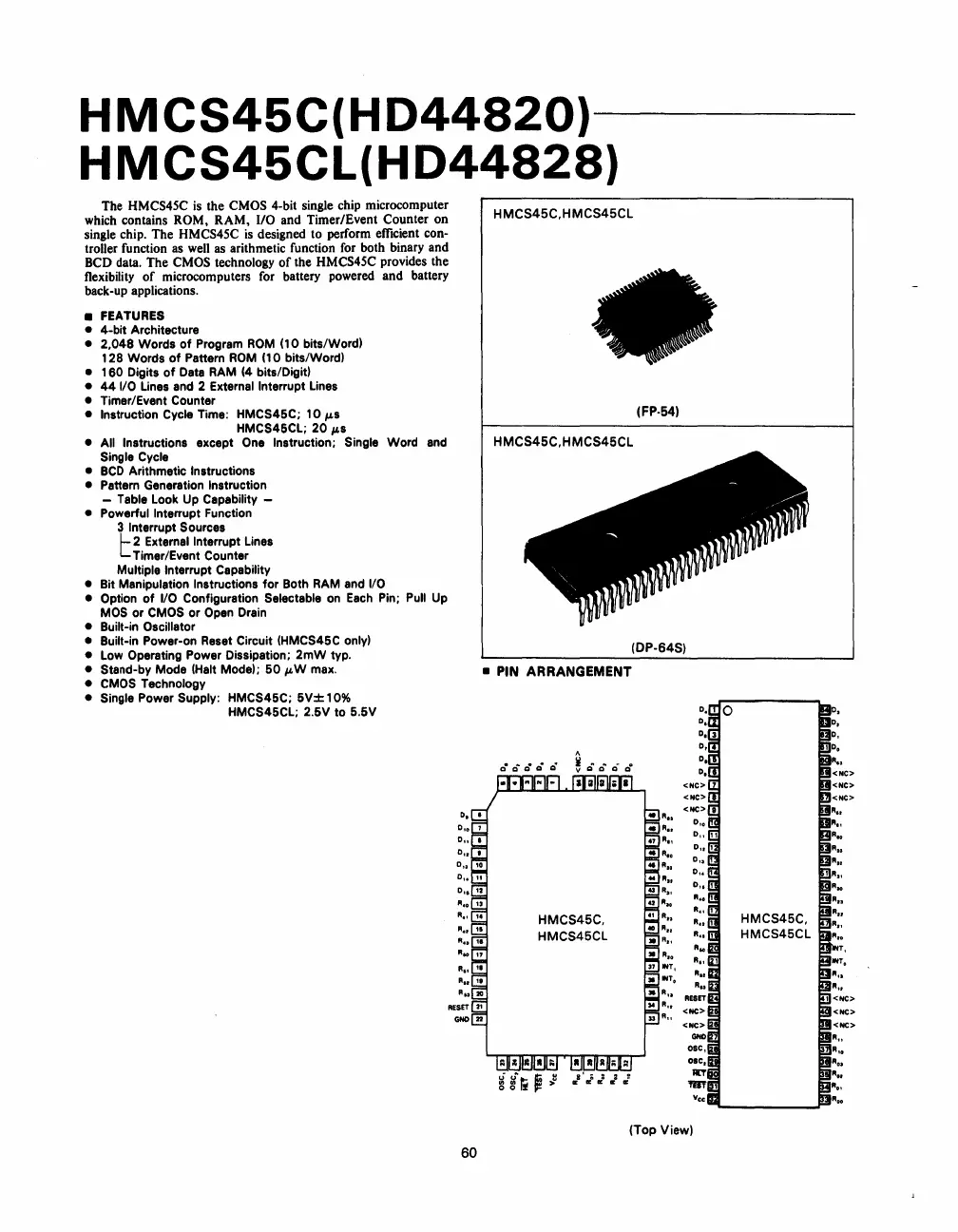

HMCS45C,HMCS45CL

(DP-64S)

•

PIN

ARRANGEMENT

GND

22

60

HMCS45C,

HMCS45CL

D.~

0

D,

D,

3

D,

D,

D,

<NC>

<NC>

<NC>

8

D"

~

DII "

D,. 1

D

..

D

tt

1

0,.1

R

••

Roll

1

R

••

1

R ... 1

R

..

R"

1

R

..

R

..

RESET

<NC>

<NC>

GND

OSC,

OSC,

JIlT

'fRf

1

Vee

(Top View)

D,

D.

D,

1

Do

R

..

<NC>

<NC>

<NC>

R

..

R"

R

..

R

..

R

..

,

R.I'

R

..

R

..

HMCS45C,

R

..

R

..

HMCS45CL

R

..

flNT,

INTo

"

..

R

..

1

<NC>

<NC>

<NC>

R"

R,.

R

..

R

..

R

..

R

..

Loading...

Loading...