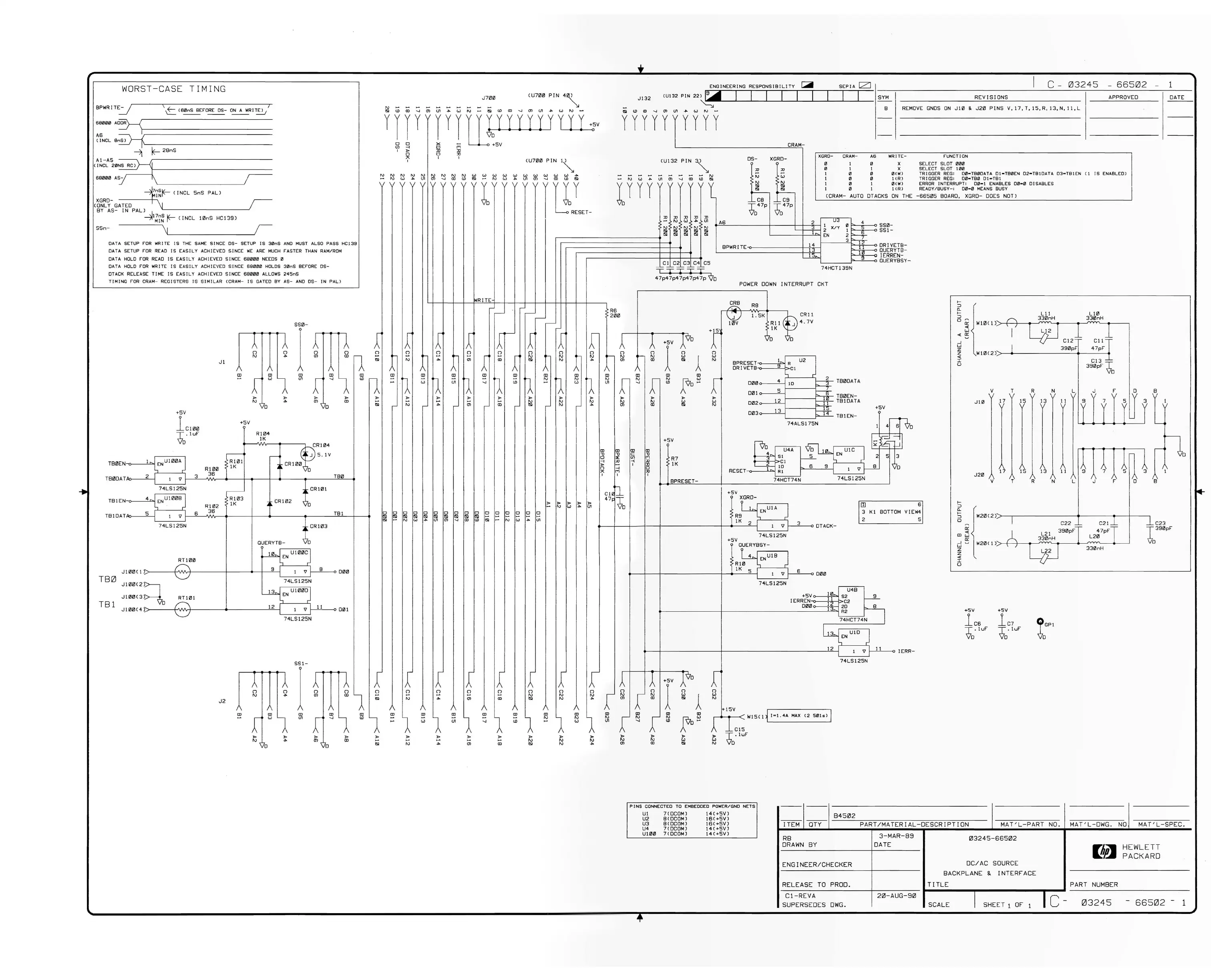

WORST-CASE TIMING

BPWRIT~

6811l1ll1ll

A~r---

________________

_

~~NCL

8~,--

________________

_

~

k-

28nS

AI-AS

~

(INCL

211lNS

RC

)

1---

-

-------------

6811l1ll1ll

AS-\

r-

~--------

----

----~

-:t7~~

(INCL

Sn5

PAL)

XGRD

-

-------f--f-,

\ I

~

(ONLY

GATED

~

/

BY

AS- I N

PAll

-1

'--------------'

--?l1~~~

~

(INCL

10nS

H

C139)

SSn-

----~

'\J

'-

__________

~;--

DATA

SETUP

FOR

WRITE

IS

THE

SAME

SINCE

DS-

S

ETUP

IS

311lnS

AND

MUST

AL

SO

PASS

HCI39

DATA

SETUP

FOR

READ

IS

EASILY

ACHIEVED

SINCE

WE

ARE

MUCH

FASTER

THAN

RAM/ROM

DAT

A

HOLD

FOR

READ

IS

EASILY

ACHIEVED

SINCE

6801110

NEEDS

0

DATA

HOLD

FOR

WR

IT

E

IS

EASILY

ACHIEVED

SINCE

68000

HOLDS

30nS

BEFORE

DS-

DTA

CK

RELEASE

TIME

IS

EASILY

ACHIEVED

SINCE

68000

ALLOWS

245nS

TIMING

FOR

'

CRAM

-

REGISTERS

IS

SIMILAR

(CRAM-

IS

GAT

ED

BY

AS-

AND

D

S-

IN

PAL)

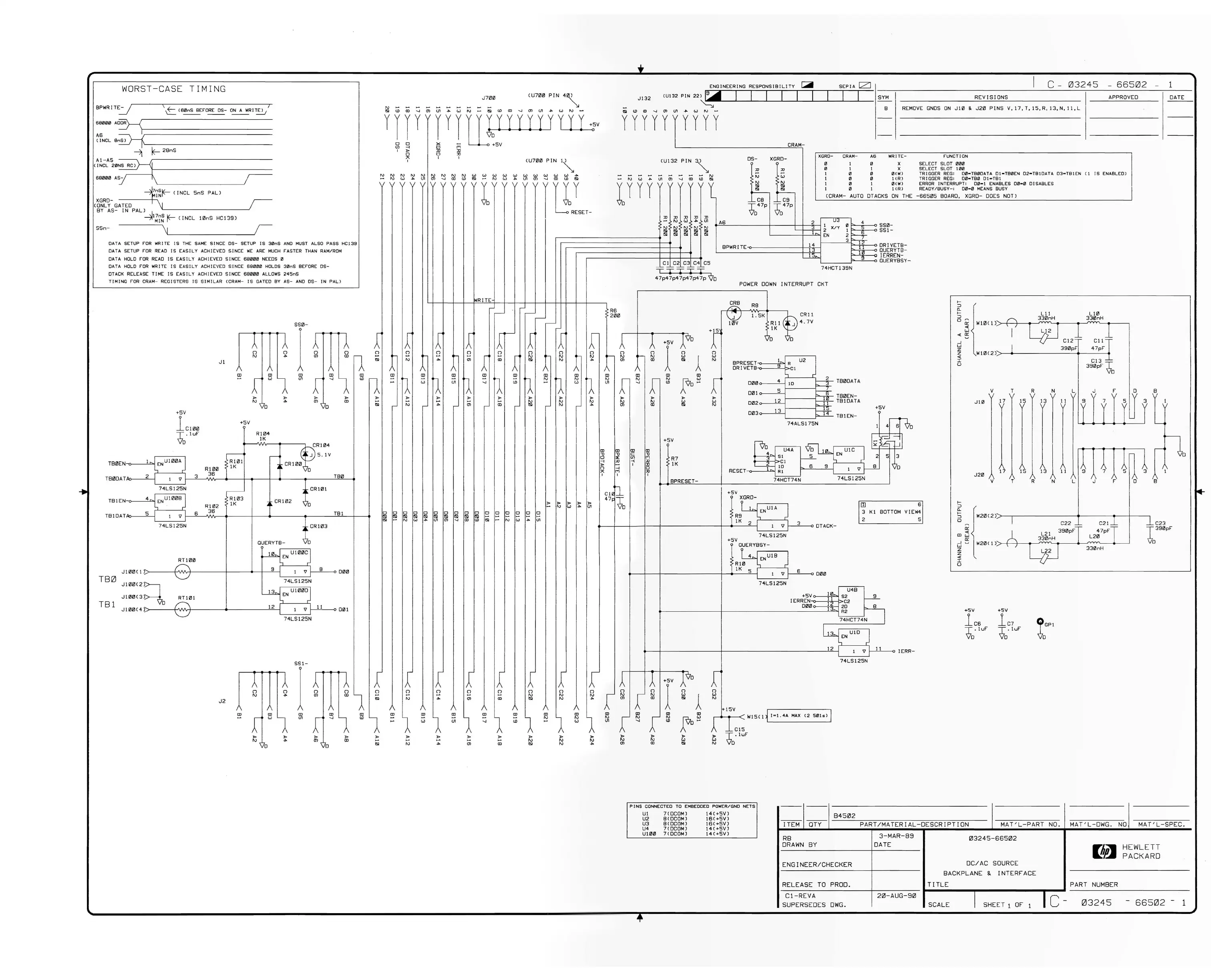

TB0EN-O--------'-'''''1

TB0DA

TI>o-_-'2"---1

3

74LSI25N

TB

I

EN-o----=

4'-""i

TB

I

DAT/lo------"S'----j

6

74

LSI2SN

RTII1II1I

RI11I0

36

RI02

36

J I

+5V

RI01

II<

RI11I3

II<

SSI1I-

RI11I4

1

aJ

U1

II<

W'

v-_----,

CR

I

111111

CR

1

1112

..

..

m

(D

o

CR104

J 5 . I V

o

CRII1II

o

TBI1I

TBI

J

1111111

( 1

),>-

----1

-'\/',1"

-+-----+--

---+---'''-----1

1-",8'-

-0

D0111

T80

T81

JI00(2)~

JII1II1I(3)

o

RT101

JII1II1I(4)>----~VY+_----~----~~~

J2

7

4L

S I2SN

1-1,-,1~-o

DI1I1

74LS

I2SN

SSI-

1

aJ

U1

o

f\)

1\.1

N N

I\)

N

N W

~

Ul m

/ \ j

N N N

"

<Xl

<0

\

\j

J70111

w w w w

IS)

..... N W

lD

\

\j

C

U70111

PIN

4~

+SV

o

ENGINEERING

JI32

s W

00

~

m

~

~

W N

llill

lili

CUl32 PIN

-

(I)

Ul

Y

~ ~

a

~ ~

N N

I\)

N N

IS

IS} lSI lSI

tSa

N

~

A6

RESPON

S

IB

ILITY

~

CRAM-

OS-

XGRO-

Is·

- -

N W

I\)

N

1Sl 1Sl

~ ~

I

C8

=:-;;-

~047P ~047P

2

SEPIA 0 I C -

03245

-

66502

1

I I

I-S-Y-M~I-------------------R-EV-I-S-I-0-N-S------------------71~~~~~A~P~P~R~O-

V

_-E_D~~~~~~--D-A-TE--

XGRD-

CRAM-

0 1

0 1

1 0

I 0

1

0

I 0

(CRAM

-

AUTO

U;:I

4

~

X/Y

III

1

B

REMOVE

GNDS

ON

JI0

&

J2111

PINS

V,

17,

T,IS

,

R,

13,N,

II

, L

A6

WRITE-

0

1

III

0

I

I

OTA

X

X

0(W)

ICR)

0(W)

ICR)

CI<S

ON

THE

SSI1I-

551-

F

UNCTION

SELECT

SLOT

000

S

ELE

CT

SLOT

11Il0

TRIGGER

REG

:

D0-TB0DATA

DI

-TB0EN

D2-TBI

DATA

D3-TBIEN

TRIGG

ER

REG:

D0-TB0

DI

-TBI

ERROR

INTERRUPT

: 00-1

ENABLES

00-0

DISABLES

READY/8USY-

:

00-0

MEANS

BUSY

-66SI1IS

BOARD,

XGRO-

DOES

NOT)

(1

IS

ENABLED

)

r-

_____________

~<SI

<SI

<SI

~

~

EN

2 r---+

3

p......p.--

\

aJ

W

...

..

-

...

\

aJ

U1

DOD DOD

0 0 0 0 0 0 0 0 0 0

~

~ ~ ~

<SI

<SI

~

<SI

1Sl

<SI

- - - - - -

~

N W

~

Ul m

~

m w

~

- N W

~

~

aJ

w

J

n

-

...

..

...

\

aJ

U1

iJ

n

..

m

I I

\

aJ

n

<Xl

..

<Xl

\

aJ

..

N

<SI

I

l>

J>o

l>

:t--

:t--

- I\J W •

U1

,

I~

l'f

[I)

aJ

N N

- W

..

..

N N

N ...

R6

2111111

[

..

N

m

..

N

m

..

I\)

(I)

CI C2

C3 C4

C 5

TTTTT-,

47p47p47p47p47p

7D

I

+SV

..

W

1Sl

t7

f

II<

1 BPRESET-

..

w

I\)

14

BPW

RITE

1;:1

IfII

L.n",.

S

74HCT139N

POWER

DOWN

INTERRUPT

CI<T

CR8

R8

1.

51<

RII

II<

o

CRIl

4.7V

BPRE5ET

-.r---~""I

DR

I VETB-.r---"'----t>

011l11l

0-

--

4

~

f----------i-,

01111

0-

__

,...,5"-l

011l2o---~12~1-----~

r-----~

0111

3

0----'-'

1

3"-1

74ALSI7SN

U4A

SI

t-----H>cl

10

RE

SET --o-----''''''i R 1

+5V

XG

RO-

7~4:-:-H-:-::

C

:-::T:-::

7

:-:4-'N

TBI1IDATA

TBI1IEN-

TBIOATA

TBIEN-

74LSI25N

rn

ORIVETB-

OUERYT8

-

IERREN-

OUERYBSY-

+SV

S 3

o

6

3

1<1

BOTTOM

VI

EW4

2 5

'V

f--,

3

,---<>

OlACI<-

'---------'

74LSI2SN

+5V

OUERYBSY-

74LS12SN

f--~6---o

0111111

U4B

+5Vo-~IHil~

S2

IERREN

1

C2

0111111

I 20

t---------------+-------------------------~~~R2

9

8

'V

f-'--'-

---o

I ERR-

'------'

n

W

N

+ISV

WIS<I

~

1-1.

4A

MAX

(2

511l1$)

I

l>

W

I\)

CIS

~O·IUF

PINS

CONN

ECTED

TO

EMBEODED

POWER

/GN

D

NETS

UI

7(OCOM)

14(+5V)

U2

8(OCOM)

16(+SV)

-----

---

----

---

74LS12SN

B4502

I-

:::l

a..

I-

:::l

Ocr

«

w

«cr

--1

W

Z

Z

«

I

u

L11

L10

c=)

33111nH

33enH

W

1111

( I

)>-

+-I-+----<iL#J

..........

L12

........

-3~-~-~--<iltF

..........

4

;~

~

~

-

t

...

i ----,

WII1I(2)>--.1----------_------jl.

CI3

~

I

39111pF

~O

V T

JII1I

Y

17

U

V

5 t

~

B

~

J2111

T\

F

~

I

§

rW2111(2)1~-.---------+_---

-

~-+_

-_.

Ql

~

~

fo~~~PF

j

~

lW2I11U)

v(

I

U

+5V

?

-LC6

~O·IUF

+5V

?

-LC7

~O·IUF

U3

8(OCOM)

16(+SV)

ITEM

on

PART/MATERIAL-DESCRIPTION

MAT

' L-PART

NO.

MAT'L-DWG.

NO

MAT'L-SPEC.

U4

7(OCOM)

14(+SV)

Ull1ll1l

7(DCOM) 14 (+SV)

RB

3-MAR-89

03245-66502

DRAWN

BY

DATE

[hpJ

HEWLETT

PACKARD

ENGINEER/CHECKER

DC

/

AC

SOURCE

BACKPLANE

&

INTERFACE

RELEASE

TO

PROD.

TITLE

P

ART

NUMBER

Cl-REVA

20-AUG-90

I

Ic-

SUPERSEDES

DWG.

SCALE

SHEET 1

OF

1

03245

-

66502

-

1

Scans by Artekmedia => 2010

Loading...

Loading...