MESSAGES

ALL

EXTERNAL

REFERENCES

MUL

TIBUSCi>

II

AND

80386

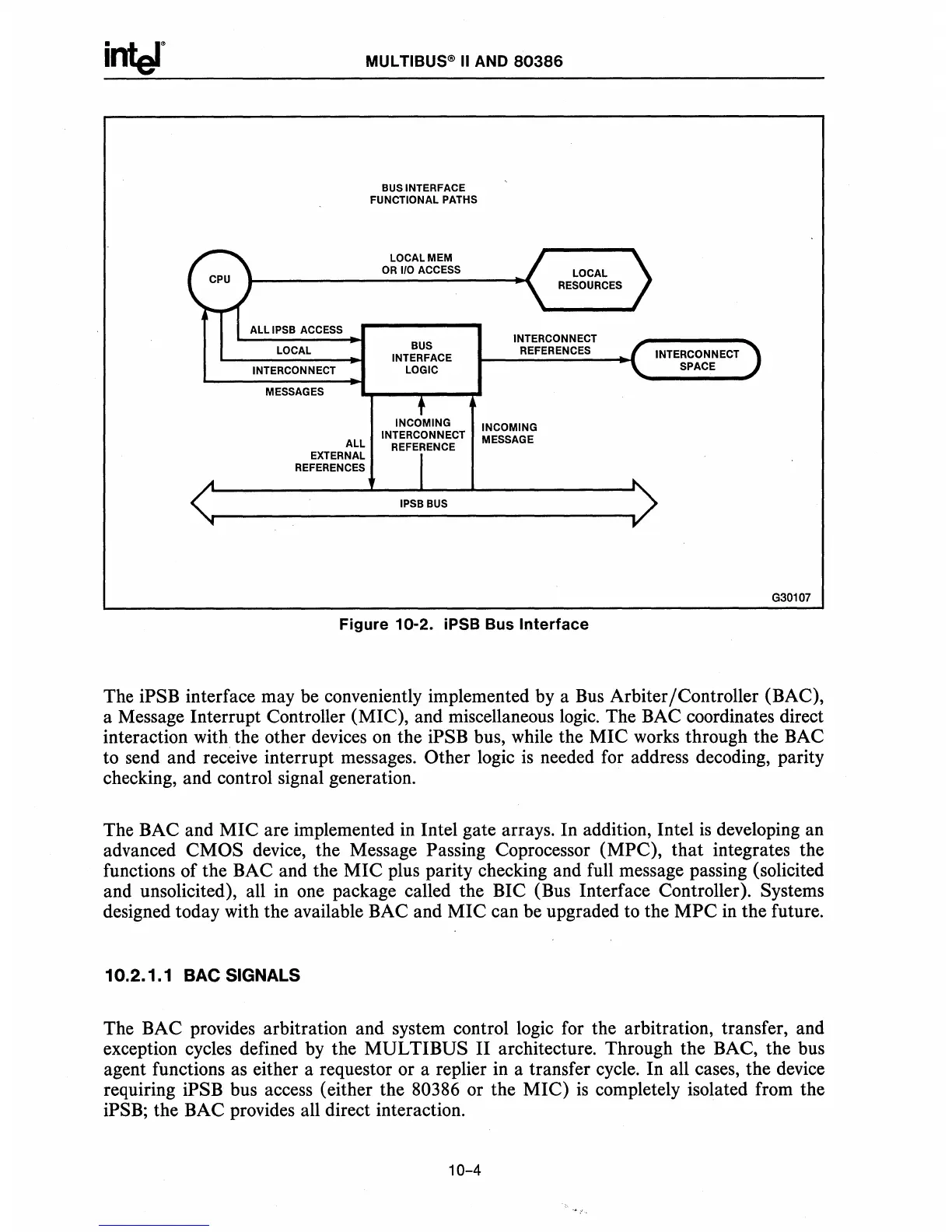

BUS INTERFACE

FUNCTIONAL PATHS

LOCALMEM

OR

I/O ACCESS

BUS

INTERFACE

LOGIC

INCOMING

INTERCONNECT

REFERENCE

IPSBBUS

INTERCONNECT

REFERENCES

INCOMING

MESSAGE

Figure 10-2. iPSB Bus

Interface

INTERCONNECT

SPACE

G30107

The iPSB interface may be conveniently implemented

by

a

Bus

Arbiter/Controller (BAC),

a Message Interrupt Controller (MIC), and miscellaneous

logic.

The BAC coordinates direct

interaction with the other

devices

on

the iPSB bus, while the MIC works through the BAC

to send and receive interrupt messages.

Other logic

is

needed for address decoding, parity

checking, and control signal generation.

The BAC and

MIC

are implemented

in

Intel gate arrays. In addition, Intel

is

developing an

advanced

CMOS device, the Message Passing Coprocessor (MPC), that integrates the

functions of the BAC and the MIC plus parity checking and full message passing (solicited

and unsolicited), all

in

one

package called the BIC (Bus Interface Controller). Systems

designed today with the available BAC and MIC can be upgraded to the MPC

in

the future.

10.2.1.1 BAC SIGNALS

The BAC provides arbitration and system control logic for the arbitration, transfer, and

exception cycles defined

by

the MUL TIBUS II architecture. Through the BAC, the bus

agent functions as either a requestor or a replier

in

a transfer cycle. In all cases, the device

requiring iPSB bus access (either the

80386 or the MIC)

is

completely isolated from the

iPSB; the BAC provides all direct interaction.

10-4

Loading...

Loading...