Summary Tables of Changes

Intel

®

Core™2 Extreme Processor X6800 and

Intel

®

Core™2 Duo Desktop Processor E6000 and E4000 Sequence 15

Specification Update

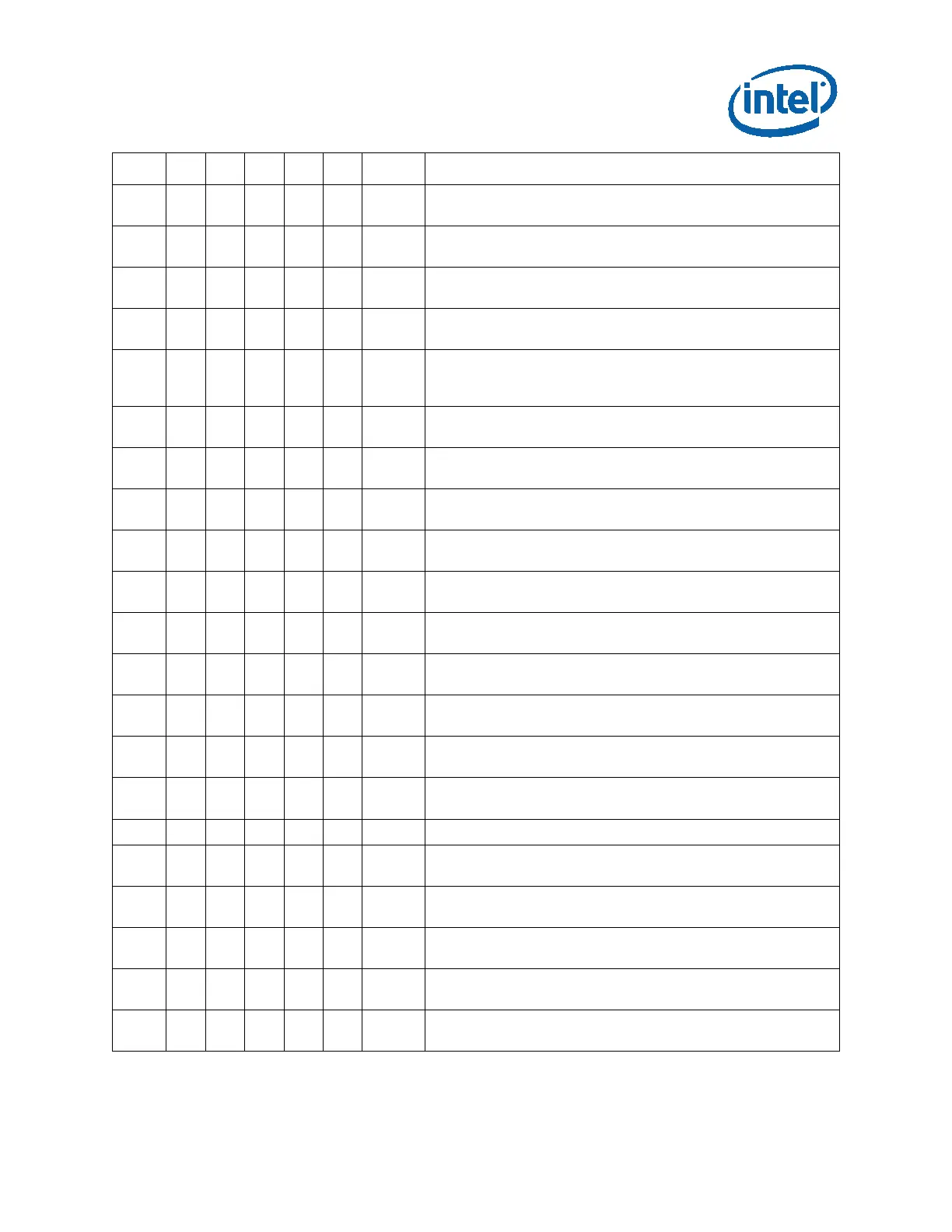

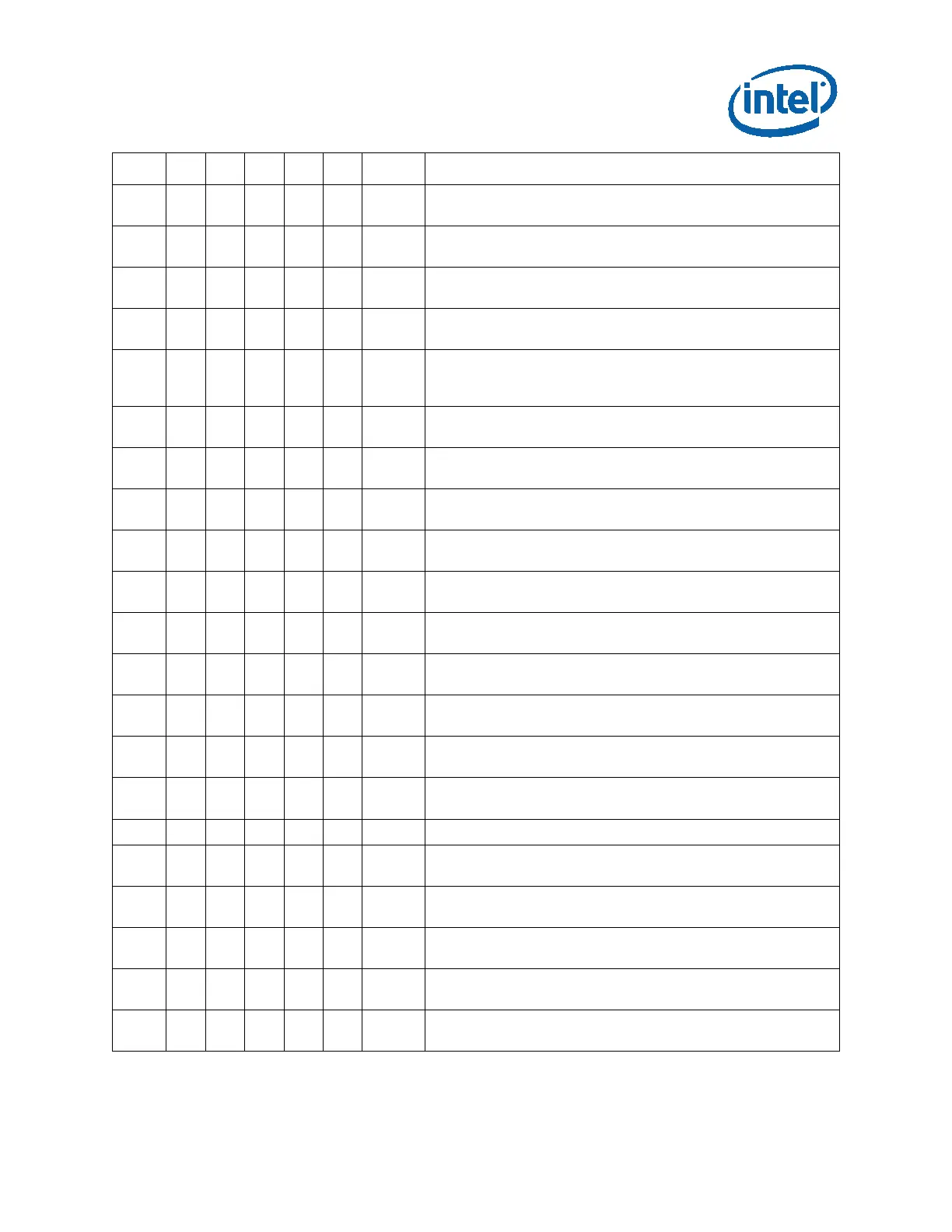

NO B1 B2 L2 M0 G0 Plan ERRATA

AI96 X X X X X No Fix

Performance Monitoring Event SIMD_UOP_TYPE_EXEC.MUL is

Counted Incorrectly for PMULUDQ Instruction

AI97 X X X X X No Fix

Storage of PEBS Record Delayed Following Execution of MOV

SS or STI

AI98 X X X X X No Fix

Store Ordering May be Incorrect between WC and WP Memory

Types

AI99 X X X X X No Fix

Updating Code Page Directory Attributes without TLB

Invalidation May Result in Improper Handling of Code #PF

AI100 X X X X Fixed

Performance Monitoring Event CPU_CLK_UNHALTED.REF May

Not Count Clock Cycles According to the Processors Operating

Frequency

AI101 X X Fixed

(E)CX May Get Incorrectly Updated When Performing Fast

String REP STOS With Large Data Structures

AI102 X X X X Fixed

Performance Monitoring Event BR_INST_RETIRED May Count

CPUID Instructions as Branches

AI103 X X X X X No Fix

Performance Monitoring Event MISALIGN_MEM_REF May Over

Count

AI104 X X X X X No Fix

A REP STOS/MOVS to a MONITOR/MWAIT Address Range May

Prevent Triggering of the Monitoring Hardware

AI105 X X X Fixed

False Level One Data Cache Parity Machine-Check Exceptions

May be Signaled

AI106 X X X X X No Fix

A Memory Access May Get a Wrong Memory Type Following a

#GP due to WRMSR to an MTRR Mask

AI107 X X X X X No Fix

PMI While LBR Freeze Enabled May Result in Old/Out-of-date

LBR Information

AI108 X Fixed

VMCALL failure due to corrupt MSEG location may cause VM

Exit to load the machine state incorrectly

AI109 X X X X Fixed

Overlap of an Intel

®

VT APIC Access Page in a Guest with the

DS Save Area May Lead to Unpredictable Behavior

AI110 X X X X X No Fix

VTPR Write Access During Event Delivery May Cause an APIC-

Access VM Exit

AI111 X X No Fix BIST Failure After Reset

AI112 X X X X X No Fix

Performance Monitoring Event FP_MMX_TRANS_TO_MMX May

Not Count Some Transitions

AI113 X No Fix

When One Core Executes SEXIT the Other Core's Last Branch

Recording May be Incorrect

AI114 X No Fix

A GETSEC[ENTERACCS] Instruction Executed Immediately after

GETSEC[WAKEUP] Instruction May Result in a Processor Hang

AI115 X X X X X No Fix

Instruction Fetch May Cause a Livelock During Snoops of the L1

Data Cache

AI116 X X X X X No Fix

Use of Memory Aliasing with Inconsistent Memory Type may

Cause a System Hang or a Machine Check Exception

Loading...

Loading...