Enhanced Serial Audio Interface (ESAI)

ESAI Programming Model

MOTOROLA DSP56367 10-13

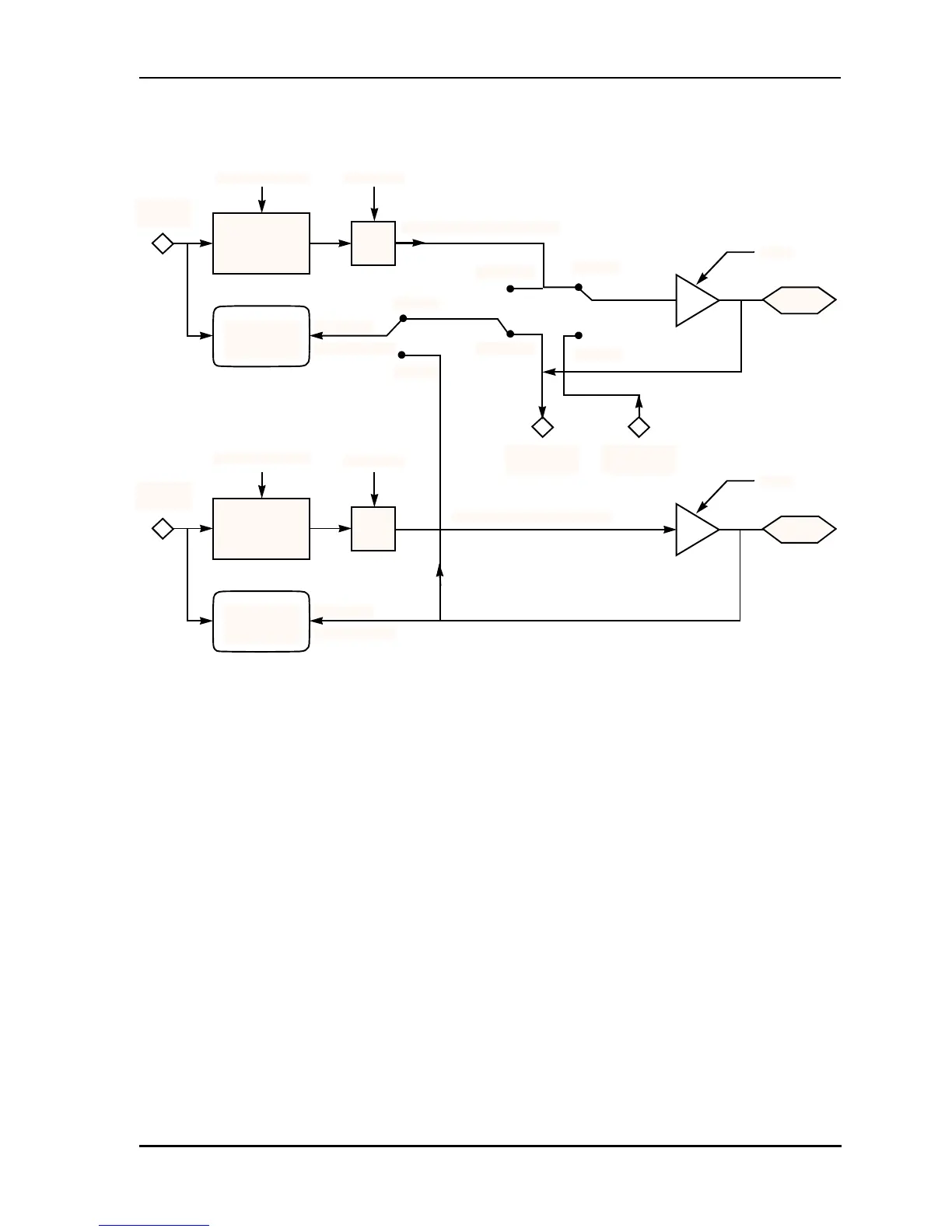

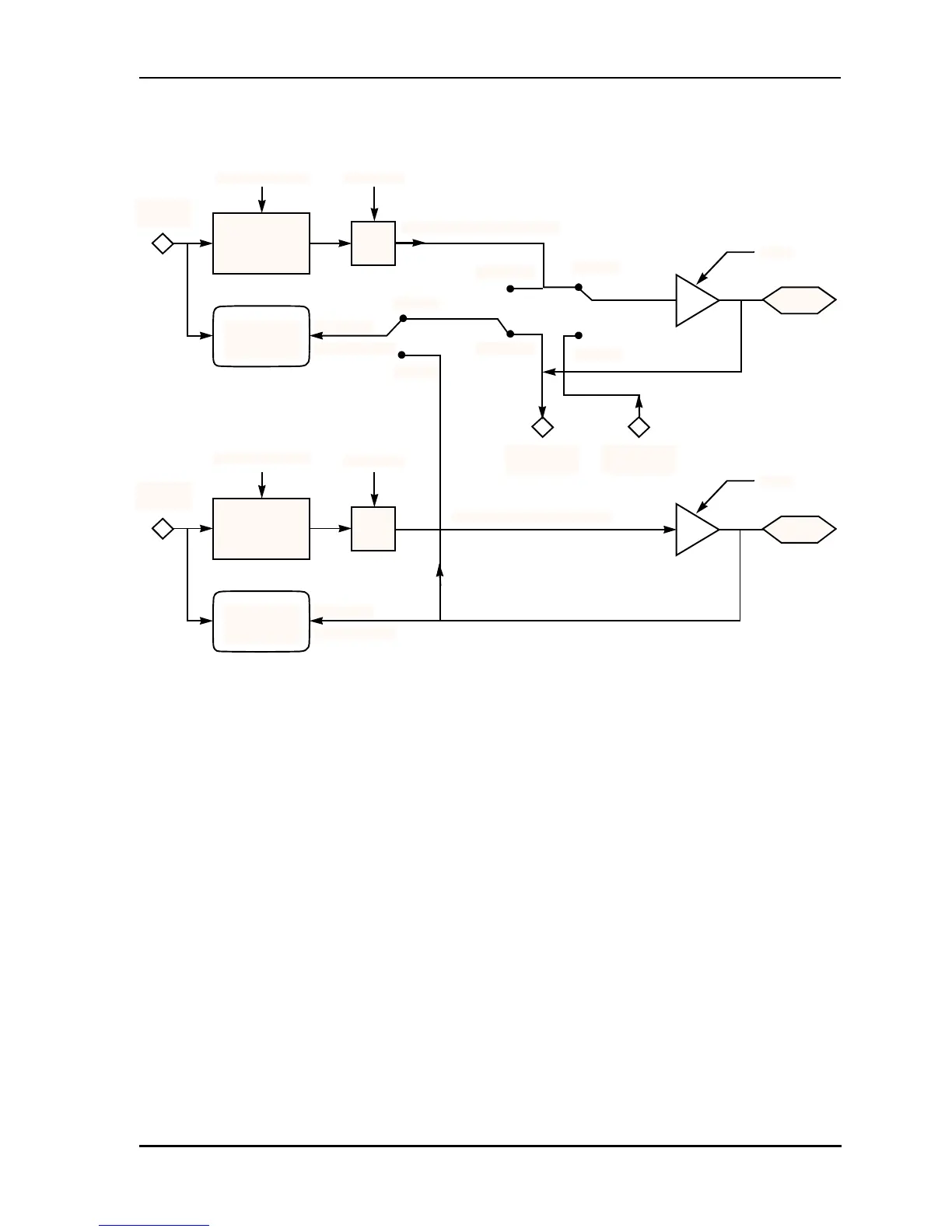

Figure 10-4 ESAI Frame Sync Generator Functional Block Diagram

10.3.1.4 TCCR Tx High Frequency Clock Divider (TFP3-TFP0) - Bits 14–17

The TFP3–TFP0 bits control the divide ratio of the transmitter high frequency clock to the

transmitter serial bit clock when the source of the high frequency clock and the bit clock is the

internal DSP clock. When the HCKT input is being driven from an external high frequency

clock, the TFP3-TFP0 bits specify an additional division ratio in the clock divider chain. See

Table 10-3 for the specification of the divide ratio. The ESAI high frequency clock generator

functional diagram is shown in Figure 10-3.

FRAME SYNC

TRANSMIT

FRAME SYNC

RECEIVE

RX WORD

CLOCK

TX WORD

CLOCK

RDC0 - RDC4

TDC0 - TDC4

RECEIVER

FRAME RATE

DIVIDER

TRANSMITTER

FRAME RATE

DIVIDER

RECEIVE

CONTROL

LOGIC

TRANSMIT

CONTROL

LOGIC

RFSL

TFSL

SYNC

TYPE

SYNC

TYPE

SYN=0

SYN=1

INTERNAL RX FRAME CLOCK

RFSD=1

SYN=1

RFSD=0

SYN=0

RFSD

FSR

TFSD

FST

INTERNAL TX FRAME CLOCK

FLAG1 IN

(SYNC MODE)

FLAG1OUT

(SYNC MODE)

Loading...

Loading...