CHAPTER 6 DMA FUNCTIONS (DMA CONTROLLER)

261

User’s Manual U14359EJ4V0UM

6.14 Times Related to DMA Transfer

The overhead before and after DMA transfer and minimum execution clock for DMA transfer are shown below. In

the case of external memory access, the time depends on the type of external memory connected.

Table 6-3. Number of Minimum Execution Clocks in DMA Cycle

DMA Cycle Number of Minimum Execution Clocks

From DMARQn signal acknowledgement to DMAAKn signal

rising

4 clocks

External memory access Depends on the memory connected.

Internal RAM access 1 clock

Remark n = 0 to 3

6.15 Maximum Response Time for DMA Transfer Request

The response time for a DMA transfer request becomes the longest under the following conditions (in the DRAM

refresh cycle enabled state). However, the case when a higher priority DMA transfer is generated is excluded.

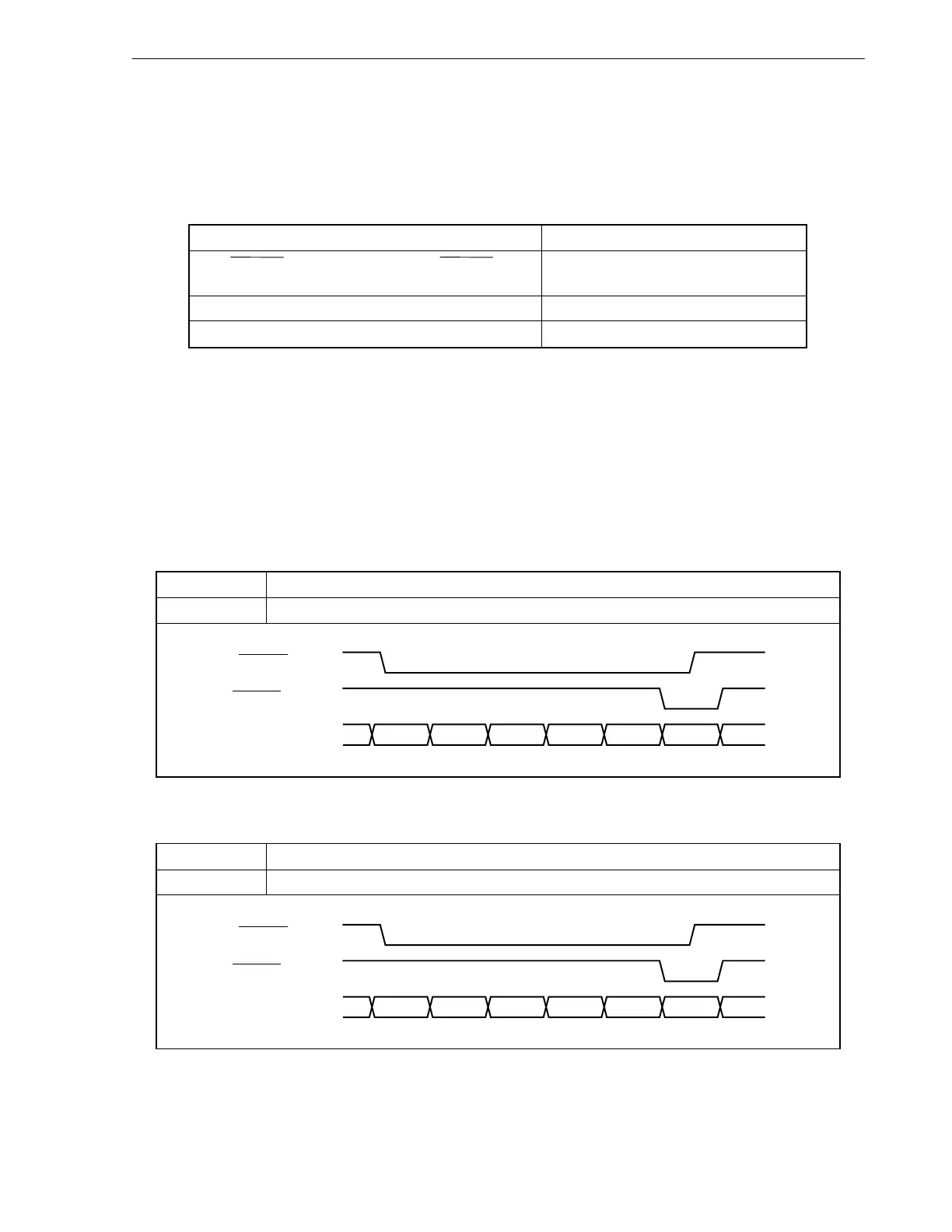

(1) Condition 1

Condition Instruction fetch from an external memory in 8-bit data bus width

Response time Tinst × 4 + Tref

DMAAKn (output)

D0 to D15 (I/O)

DMARQn (input)

DMA cycleRefresh

Fetch (1/4) Fetch (2/4) Fetch (3/4) Fetch (4/4)

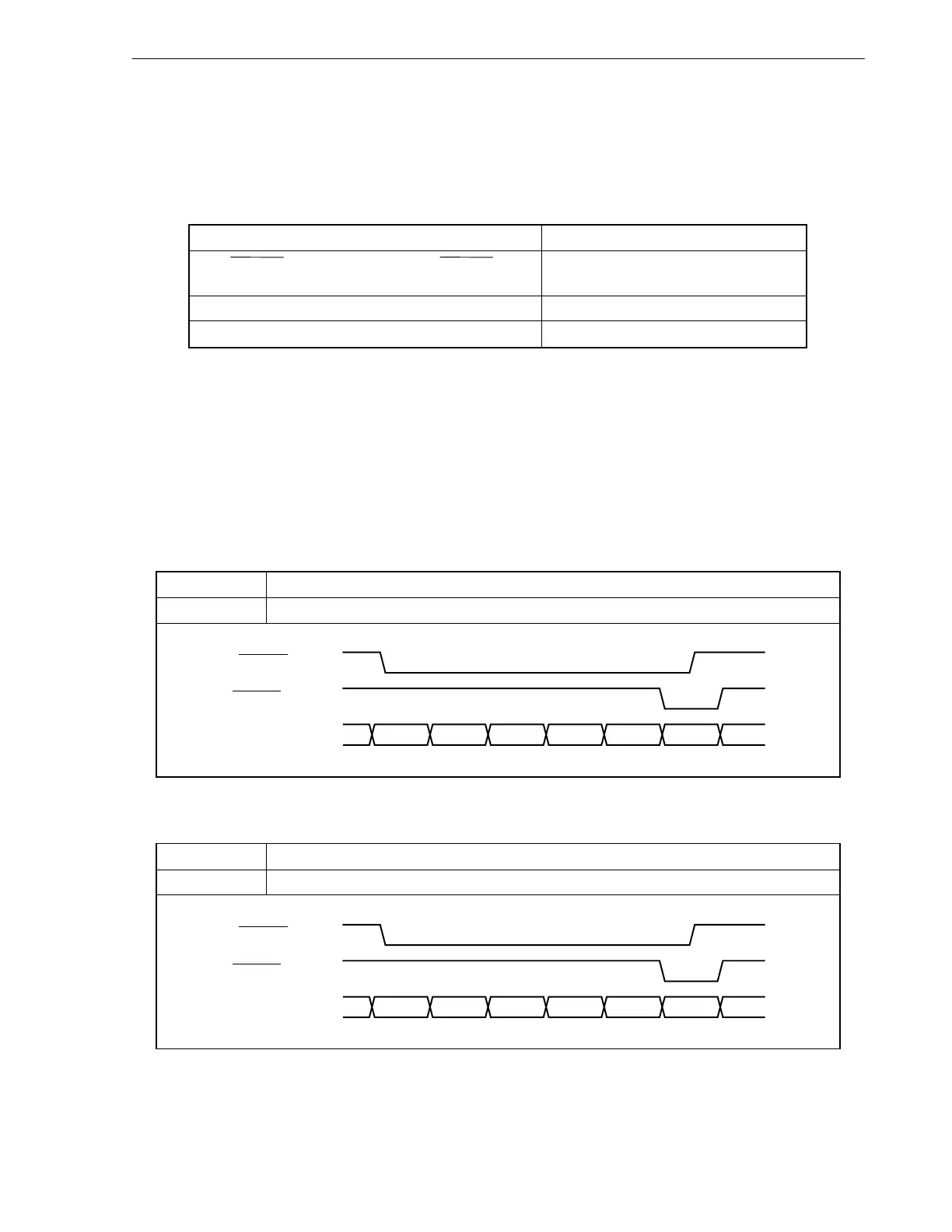

(2) Condition 2

Condition Word data access with an external memory in 8-bit data bus width

Response time Tdata × 4 + Tref

DMAAKn (output)

D0 to D15 (I/O)

DMARQn (input)

DMA cycleRefresh

Data (1/4) Data (2/4) Data (3/4) Data (4/4)

Loading...

Loading...