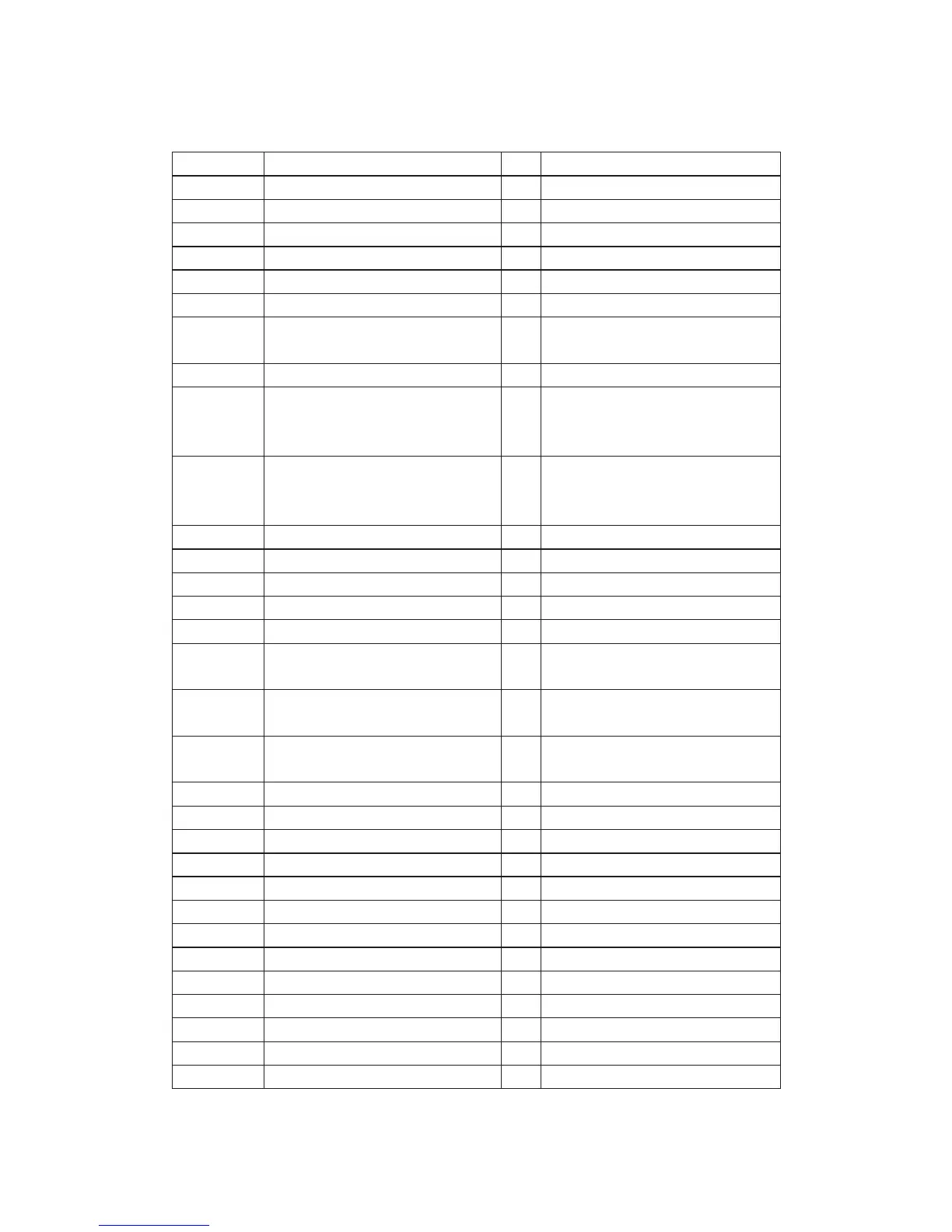

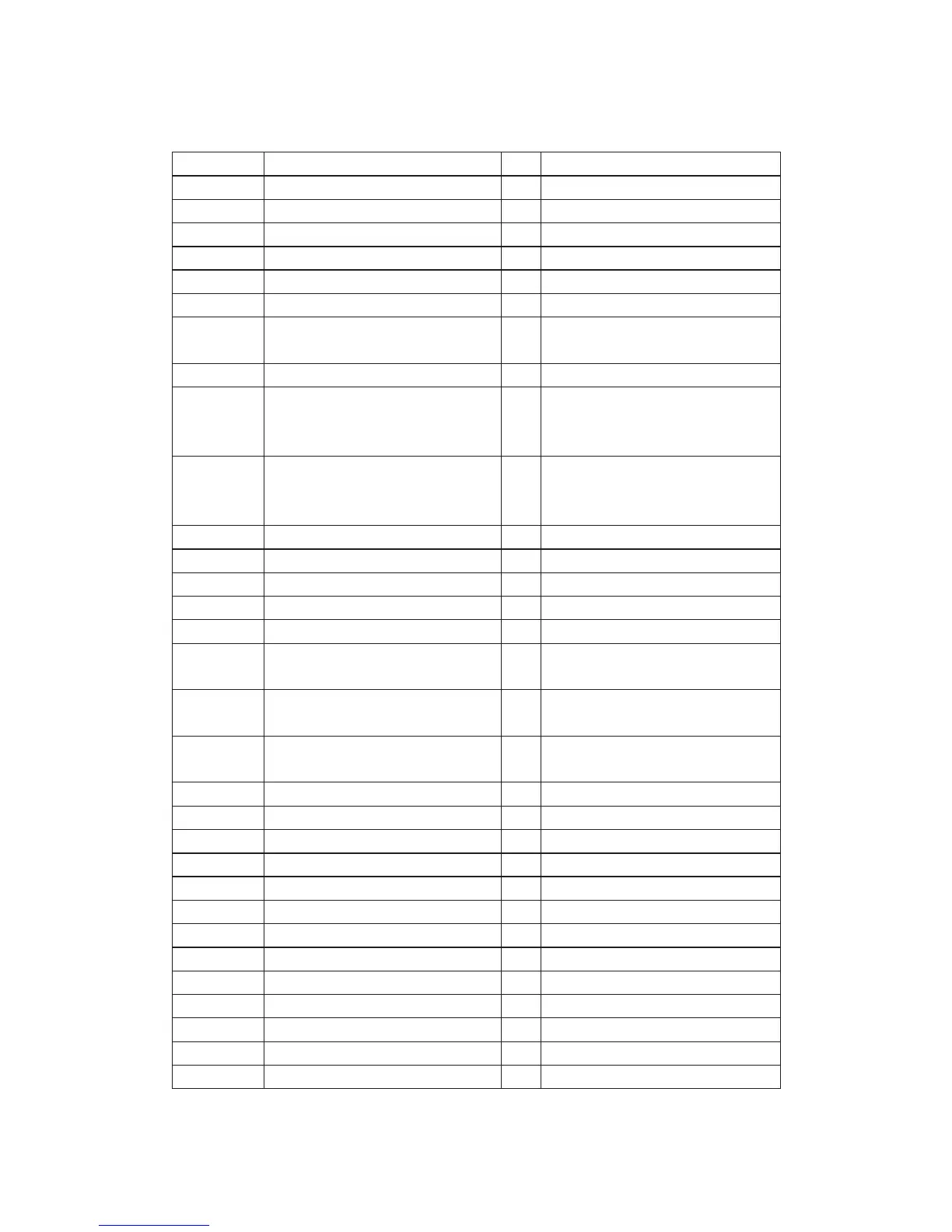

Name Number I/O Definition

DB[15:0] 96:93,90:85,82:77 I/O DRAM data bus.

DCS[1:0]# 97,100 O SDRAM chip select [1:0], active low

DQM 101 O Data input /output mask.

DSCK 102 O Clock to SDRAM.

DCLK 105 I Clock Input (27 MHz)

YUV[7:0] 115:113,110:106 O 8-bit YUV output.

PCLK2XSC

N

116 I/O

2X pixel clock.

PCLKQSCN 117 I/O Pixel clock.

VSYNCH# 118 I/O

Vertical synch for screen video

interface, programmable for rising or

falling edge, active low.

HSYNCH# 119 I/O

Horizontal sync for screen video

interface, programmable for rising or

falling edge, active low.

HD[15:0] 141:140,137:131,128:122 O Host data bus

HCS1FX# 152 O Host select 1.

HCS3FX# 153 O Host select 3.

HIOCS16# 151 I Device 16-bit data transfer.

HA[2:0] 158,155:154 I/O Host address bus.

VPP 159 I

Peripheral protection voltage. See

App Note 2.

HWR#/DCI_ACK#

149 I,O

Host write/DCI Interface Acknowledge

Signal, active low.

HRD#/DCI_CLK

150

O,

O

Host read/DCI Interface Clock.

HD[15:0] 141:140,137:131,128:122 I/O Host data bus.

HWRQ# 142 O Host write request.

HRDQ# 143 O Host read request.

HIRQ 144 I/O Host intrrupt.

HRST# 145 O Host reset.

HIORDY 146 I Host I/O ready

AUX[7:0] 169:165,162:160 I/O Auxiliary ports.

LOE# 170 O Device output enable, active low.

LCS[3:0]# 176:173 O Chip select [3:0], active low.

LD[15:0] 197:194,191:185,182:178 I/O Device data bus.

LWRLL# 198 O Device write enable, activ e low.

LWRHL# 199 O Device write enable, active low.

NC 37,38,42,203:202 No Connect pins. Leave open.

15

Loading...

Loading...