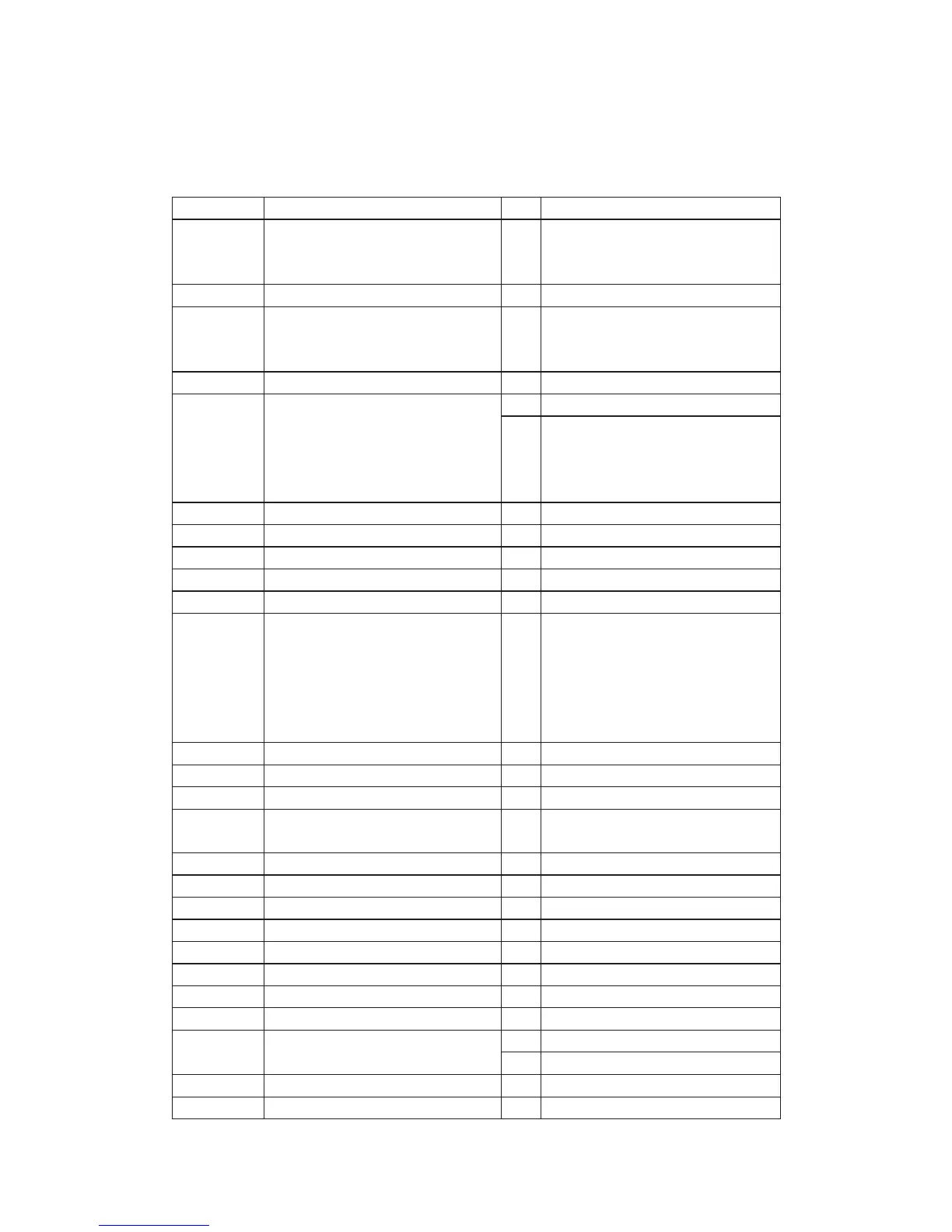

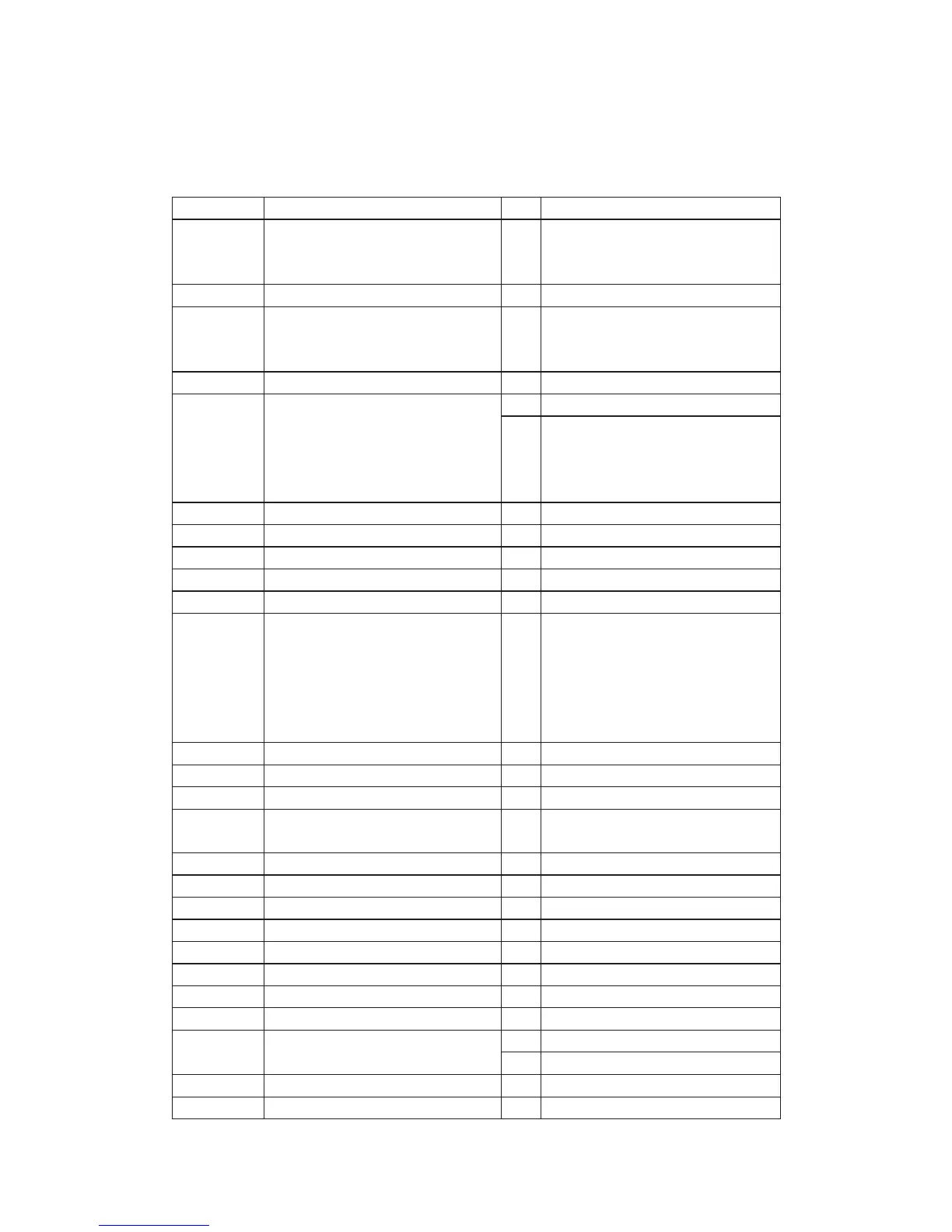

VS3811 PIN ASSIGNMENTS

Name Number I/O Definition

VCC

1,9,18,27,35,44,51,59,68,75,83,92,99

, 104, 111,121,130,139,148,157,164,

172, 183, 193,201

I

3.6 V power s upply.

LA[21:0] 23:19,16:10,7:2,207:204 O Device address output.

VSS

8,17,26,34,43,52,60,67,76,84,91,98,1

03,112,120,129,138,147,156163,171,

177,184,192,200,208

I

Ground.

RESET# 24 I Reset input, active low.

O TDM transm it data.

TDMDX

RSEL

25

I

ROM Select

RSEL Selection

0 16-bit ROM

18-bitROM

TDMDR 28 I TDM receive data.

TDMCLK 29 I TDM clock input.

TDMFS 30 I TDM frame synch.

DMTSC# 31 O TDM output enable, active low.

TWS 32 O Audio transmit fram e sync.

SEL PLL[2:0] 33 I

Selec t Pll1.

SEL-PLL2 S EL-PLL0 Clock Output

0 0 2.5*DCLK

0 1 3*DCLK

1 0 3.5*DCLK

1 1 4*DCLK

TSD[3:0] 38,37,36,33 O Audio transm it serial data port.

MCLK 39 I/O Audio m aster clock for audio DAC.

TBCK 40 I/O Audio transm it bit clock.

SPDIF DOB

M

41 O

S/PDIF (IEC958) Format O utput.

RSD 45 I Audio receive serial data.

RW S 46 I Audio receive frame synch.

RBCK 47 I Audio receive bit clock.

APLLCAP 48 I Analog PLL Capacitor.

XIN 49 I Crystal input.

XOUT 50 O Crystal output.

DMA[11:0] 66:61,58:53 O DRAM address bus.

DCAS# 69 O Column address strobe, active low.

O Output enable, active low.DOE#

DSCK EN

70

I

Clock Enable, active low.

DW E # 71 O DRAM write enable, active low.

DRAS[2:0]# 74:72 O Row address s trobe, active low.

14

Loading...

Loading...