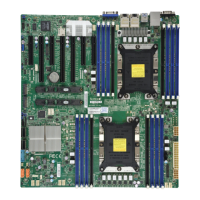

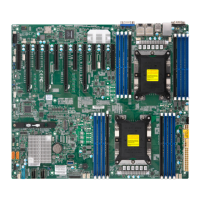

55

Chapter 2: Installation

JBMC_DEBUG

SRW1

JSDCARD1

JM2_1

JUIDB1

JP3

FAN5FAN6

FAN4

FAN3

FAN2

FAN1

JBT1

LE3

LE1

C

A

LEDM1

LE2

JNVI2C1

JIPMB1

JNVI2C2

JPME2

JPME1

T-SGPIO3

BT1

+

JSTBY1

JD1

1

JL1

JP2

JF1

JPWR1

JPWR2

JPI2C1

JPWR3

JTPM1

JRK1

JSXB1_2

JAOM

JSXB1_1

JSXB1_3

BAR CODE

X11DDW-L

REV:1.02

MAC CODE

DESIGNED IN USA

BIOS LICENSE

I-SATA 4~7

I-SATA 0~3

S-SATA 0~3

P1_NVME1

P1_NVME0

P2_NVME1

P2_NVME0

CPU2_PORT2ACPU2_PORT2BCPU2_PORT2CCPU2_PORT2DCPU1_PORT3CCPU1_PORT3DCPU1_PORT3CCPU1_PORT3D

CPU1_PORT3BCPU1_PORT3ACPU1_PORT3BCPU1_PORT3A

SXB1B:CPU1 PCI-E 3.0 X16 + CPU2 PCI-E 3.0 X16

CPU2_PORT3

SXB2:CPU2 PCI-E 3.0 X16

USB4/5(3.0)

USB0/1(3.0)

USB2/3

(3.0)

S-SATA5

S-SATA4

VGA

LAN1

LAN2

X NMIPWR

LED

NIC HDD

LED

NIC

2 1

UID

LED

PS

FAIL

PWRRST

ON

IPMI_LAN

JWD1

JBR1

C621

10G PHY

BMC

CPU1

CPU2

P2 DIMM D1

P2 DIMM E1

P2 DIMM F1

P2 DIMM C1

P2 DIMM B1

P2 DIMM A1

P1 DIMM F1

P1 DIMM E1

P1 DIMM D1

P1 DIMM A1

P1 DIMM B1

P1 DIMM C1

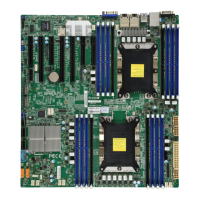

JPL1

4-pin BMC External I

2

C Header

A System Management Bus header for IPMI 2.0 is located at JIPMB1. Connect the appropriate

cable here to use the IPMB I

2

C connection on your system. Refer to the table below for pin

denitions.

External I

2

C Header

Pin Denitions

Pin# Denition

1 Data

2 Ground

3 Clock

4 No Connection

Chassis Intrusion

A Chassis Intrusion header is located at JL1 on the motherboard. Connect an appropriate

cable from JL1 to the chassis so that you can be informed of a chassis intrusion (via IPMI)

when the system case is opened. Refer to the table below for pin denitions.

Chassis Intrusion

Pin Denitions

Pin# Denition

1 Intrusion Input

2 Ground

1. SMBus

2. Chassis Intrusion

1

2

Loading...

Loading...