Control Register File Extensions

CPU Data Paths and Control2-24 SPRU733

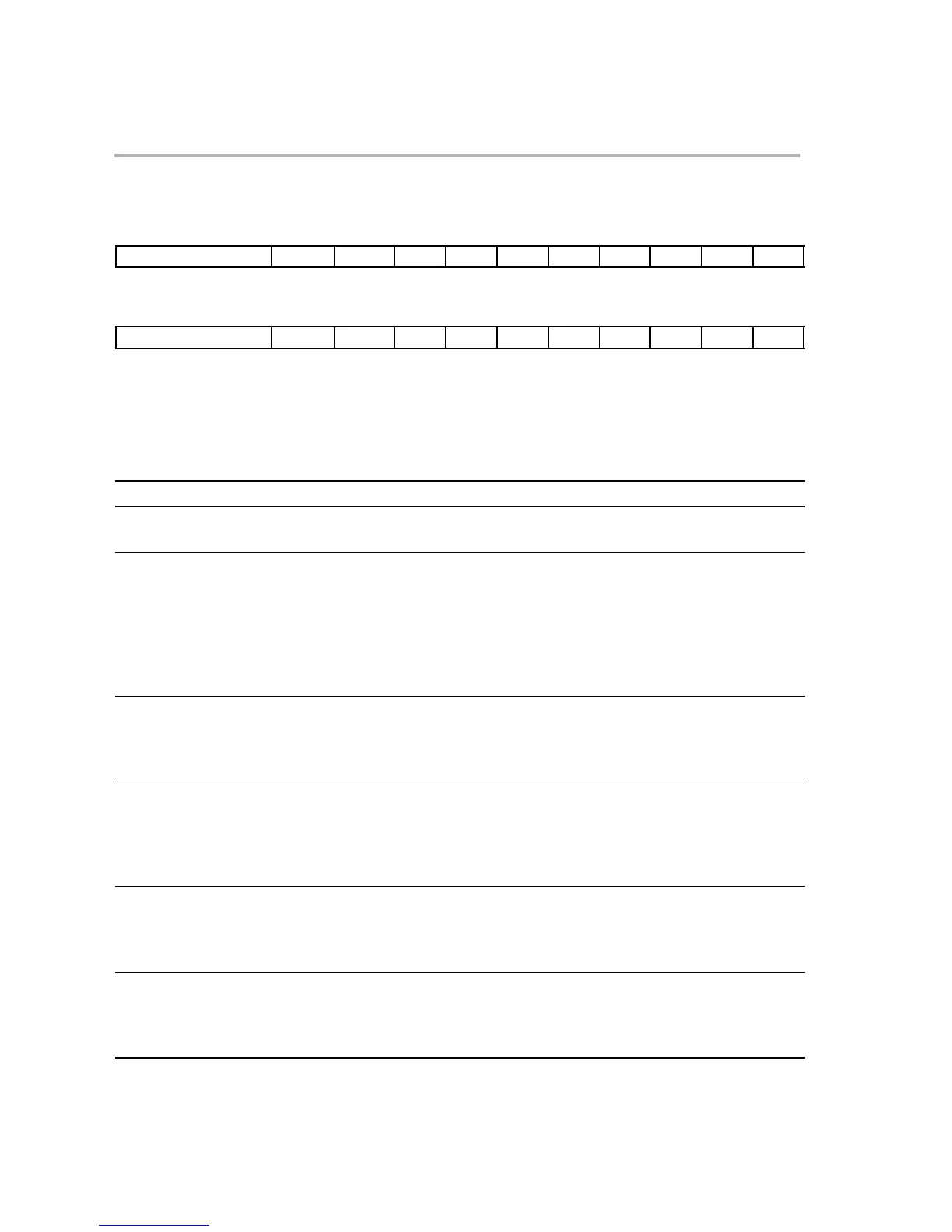

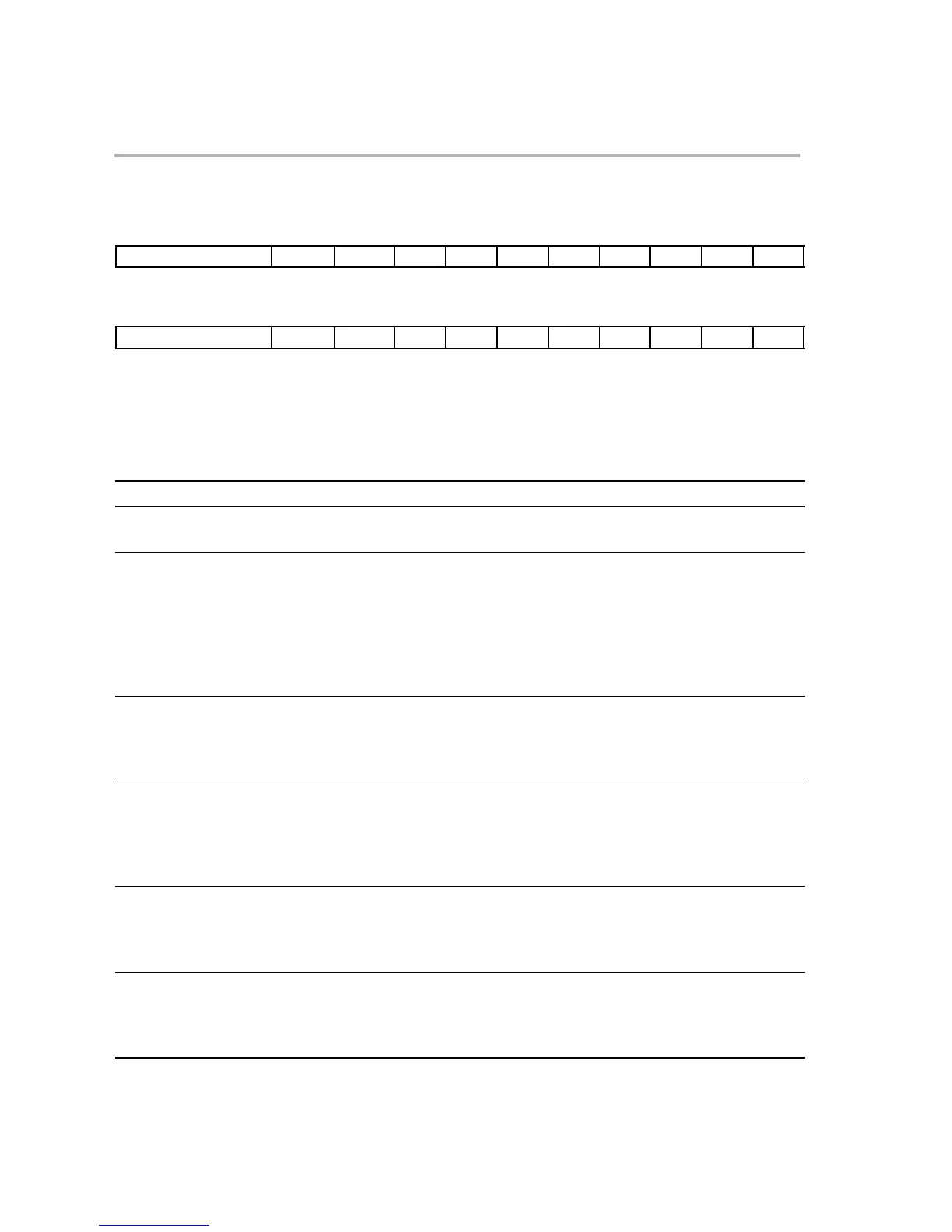

Figure 2−14. Floating-Point Adder Configuration Register (FADCR)

31 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

RMODE UNDER INEX OVER INFO INVAL DEN2 DEN1 NAN2 NAN1

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

15 111098 76543210

Reserved

RMODE UNDER INEX OVER INFO INVAL DEN2 DEN1 NAN2 NAN1

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

Legend: R = Readable by the MVC instruction; W = Writeable by the MVC instruction; -n = value after reset

Table 2−14. Floating-Point Adder Configuration Register (FADCR)

Field Descriptions

Bit Field Value Description

31−27 Reserved 0 Reserved. The reserved bit location is always read as 0. A value written to this

field has no effect.

26−25 RMODE 0−3h Rounding mode select for .L2.

0 Round toward nearest representable floating-point number

1h Round toward 0 (truncate)

2h Round toward infinity (round up)

3h Round toward negative infinity (round down)

24

UNDER Result underflow status for .L2.

0 Result does not underflow.

1 Result underflows.

23

INEX Inexact results status for .L2.

0

1 Result differs from what would have been computed had the exponent range

and precision been unbounded; never set with INVAL.

22

OVER Result overflow status for .L2.

0 Result does not overflow.

1 Result overflows.

21

INFO Signed infinity for .L2.

0 Result is not signed infinity.

1 Result is signed infinity.

Loading...

Loading...