15

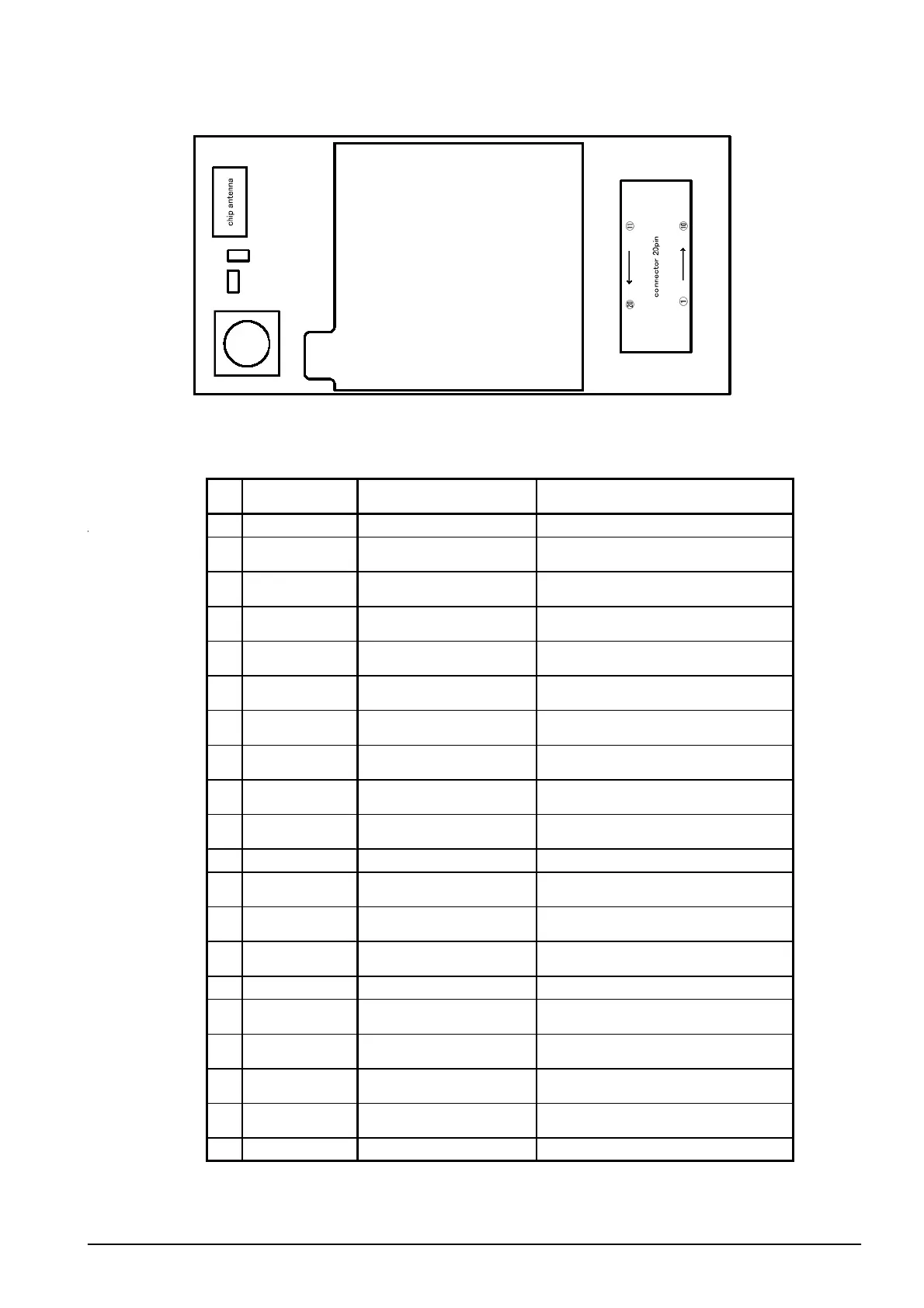

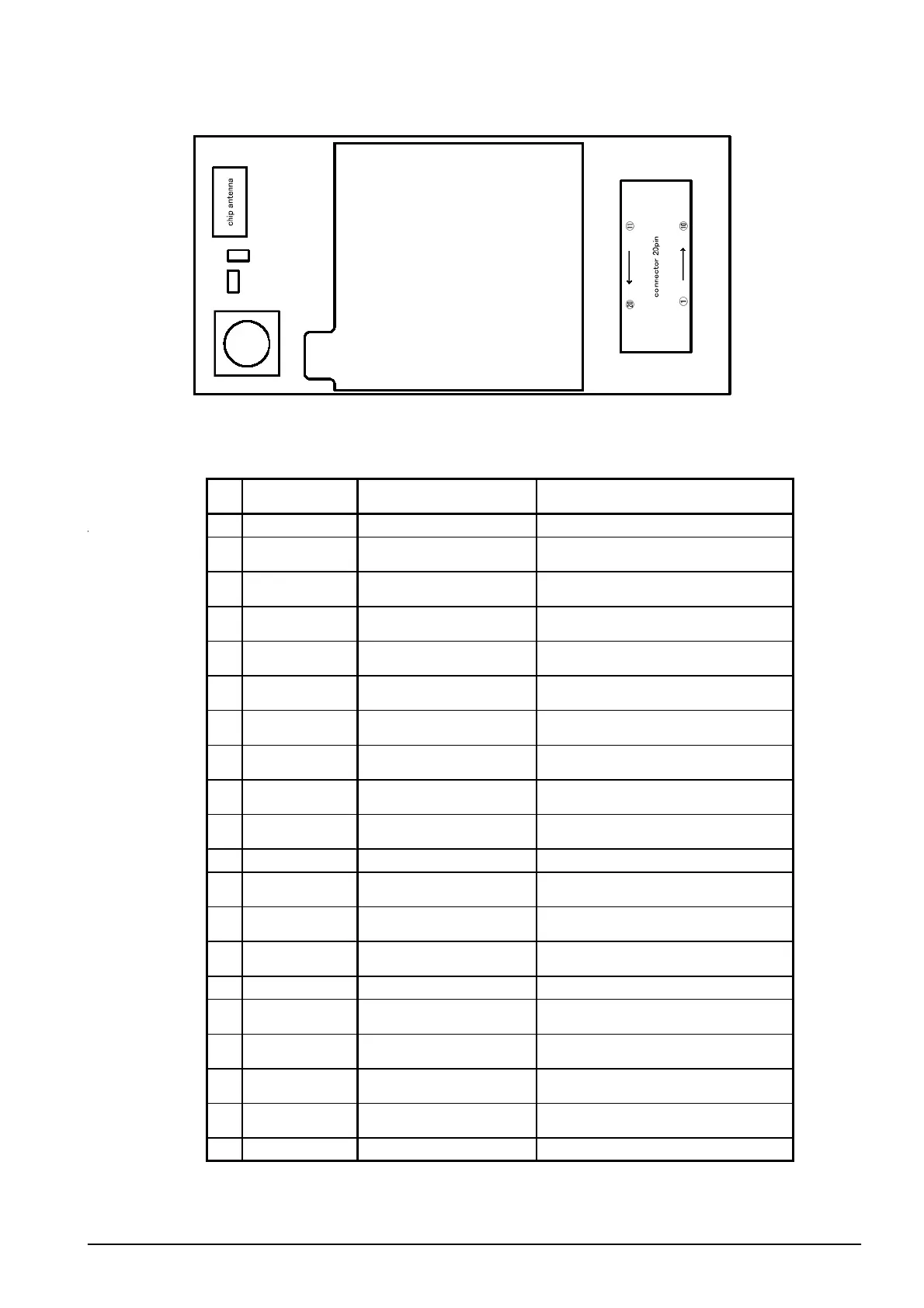

7.1.3. 端子配列

端子説明

端子

番号

端子記号 タイプ 端子説明

1GND

GND グランド

2PCMOUT

CMOS出力、内部弱プルダウン

付きでトライステート可能

PCMデータ出力

3PCMIN

CMOS入力、内部弱プルダウン

付き

PCMデータ入力

4PIO[1]

双方向、プログラマブル、内部強

プルアップ/ダウン付き

プログラマブル入出力ライン

5PIO[4]

双方向、プログラマブル、内部強

プルアップ/ダウン付き

プログラマブル入出力ライン

6UARTRX

CMOS入力、内部弱プルダウン

付き

UARTデータ入力

7 UARTTX

CMOS出力、内部弱プルアップ

付きでトライステート可能

UARTデータ出力

8RST

CMOS入力

High時リセット。入力がデバウンスされる ので、リセットにする ため

に5ms以上Highにして下さい。

9PIO[3]

双方向、プログラマブル、内部強

プルアップ/ダウン付き

プログラマブル入出力ライン

10 SPICSB

CMOS入力、内部弱プルアップ

付き

SynchronousSerialInterface用チップ選択、

アクティブLow

11 GND

GND グランド

12 UARTRTS

CMOS出力、内部弱プルアップ

付きでトライステート可能

UART送信リクエスト、アクティブLow

13 SPICLK

CMOS入力、内部弱プルダウン

付き

SerialPeripheralInterfaceクロック

14 UARTCTS

CMOS入力、内部弱プルダウン

付き

UART送信クリア、アクティブLow

15 PCMSYNC

双方向、内部弱プルダウン PCMデータ同期

16 PIO[2]

双方向、プログラマブル、内部強

プルアップ/ダウン付き

プログラマブル入出力ライン

17 SPIMOSI

CMOS入力、内部弱プルダウン

付き

SerialPeripheralInterfaceデータ入力

18 PCMCLK

双方向、内部弱プルダウン付き PCMデータクロック

19 SPIMISO

CMOS出力、内部弱プルダウン

付きでトライステート可能

SerialPeripheralInterfaceデータ出力

20 VDD

VDD 電源電圧

Loading...

Loading...