83

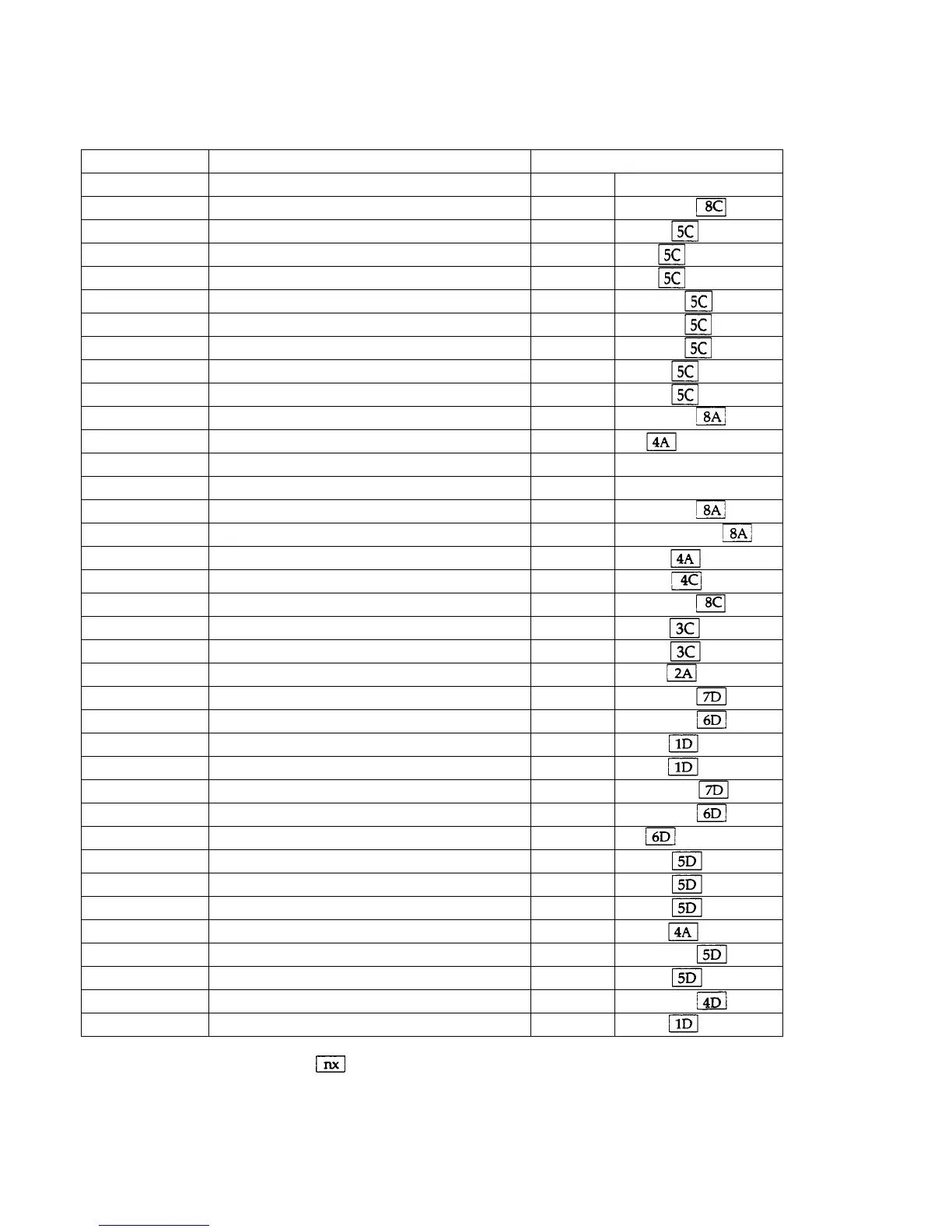

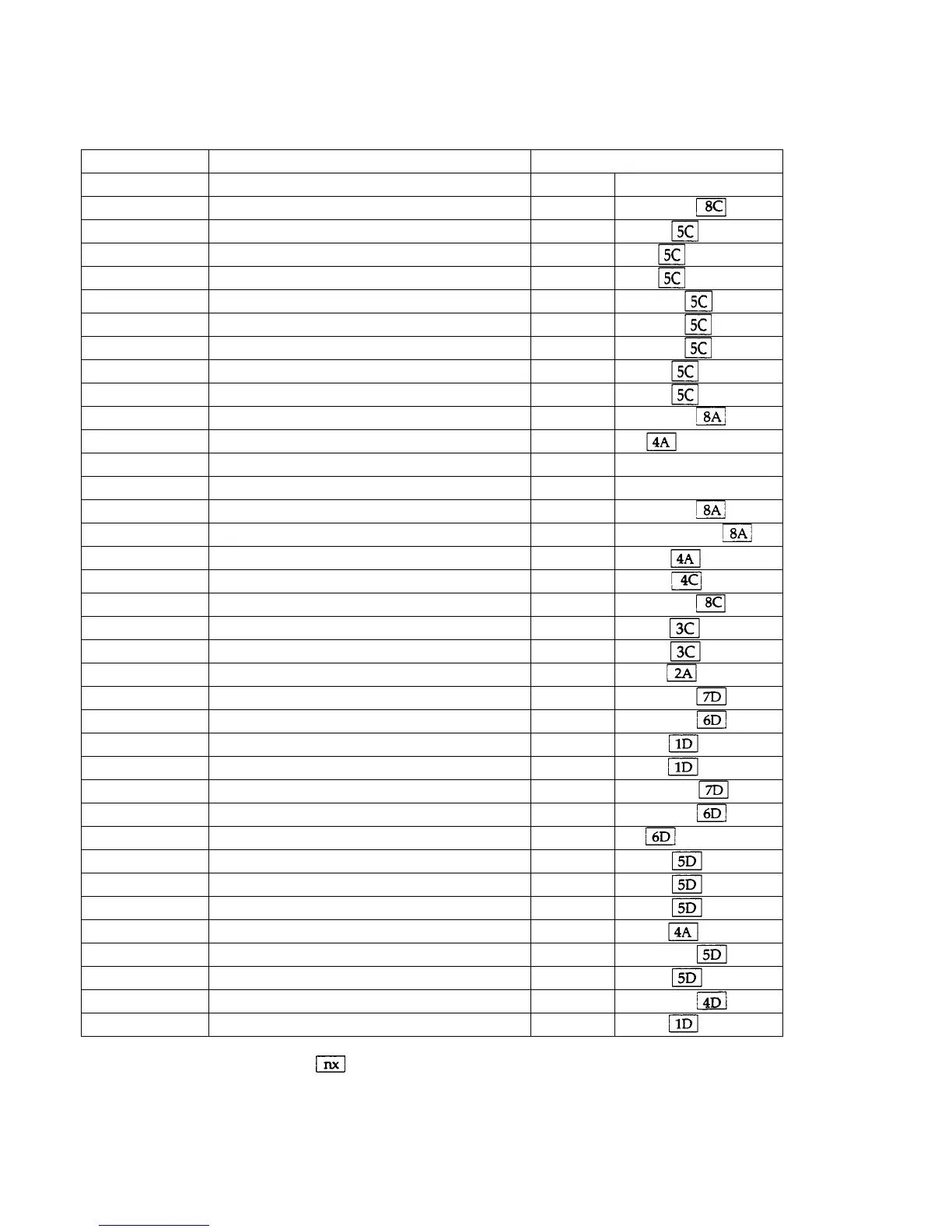

Table 6-3. Schematic Diagram, Intra-Sheet Signals

Signal Location

Mnemonic Function

1

Sheet Coordinates

CAL_LOCK Software calibration lockout (D) 2

2D,

CSP0* Test point 2

, 8C

CSP1* GP-IB interface write (D) 2

, 6B, 8C

CSP2* GP-IB interface read (D) 2

, 6B, 8C

CSP3* Keyboard readback chip select (D) 2

3D,

,6B

CSP4* Keyboard driver chip select (D) 2

3C,

, 8C

CSP5* Display driver (D) chip select bit (D) 2

3B,

, 8C

CSP6* Test point 2

, 8C

CSP7* Test point 2

,8C

EEPON* EEPROM power-on disable (D) 2

2A,

EP

Primary

µP clock (D)

2

, 5B, 5C,6B

L0 Logic zero (ground) 2 6B, 7B, 8B

L1 Logic one ( + 5 V) 2 4A, 8B

PCLR Primary power-on clear (D) 2

7B,

PCLR* Primary power-on (D) 2

1A, 4A, 3C,

R/W* RAM read/write enable (D) 2

, 6B

SA GATE

Primary

µP SA gate (D)

2

, 8C

SA MODE

Primary

µP SA mode enable (D)

2

4A,

TLRST* Trigger latch reset (D) 2

, 6D

TRIGEN Trigger enable/disable (D) 2

,7C

TRIG IN External trigger input (D) 2

, 8D

TRIG OUT Trigger output (D) 2

2A,

CC_EN* CC mode enable (D) 3

3C,

CS2* Slew rate latch select (D) 3

, 8C

CS5* Control signals latch select (D) 3

, 6D

CS6* Control signals latch select (D) 3

5D ,

CV_EN* Enable CV mode (D) 3

3C,

E

Secondary

µP clock (D)

3

, 6A ,5A, 4A

FSEL0 Transient generator frequency select bit (D) 3

, 4

FSEL1 Transient generator frequency select bit (D) 3

, 4

FSEL2 Transient generator frequency select bit (D) 3

, 4

HIGH* Enable transient DAC output (D) 3

, 7

LCLR* Clear status latch (D) 3

3D,

P_TRIG Pulse trigger (D) 3

, 6

PULSE_EN Enable pulse mode (D) 3

6A,

RCK_LOW* Loads transient generator counter (D) 3

, 7A

1

(A) = analog (D) = digital = signal origin

Loading...

Loading...