142 Chapter 3

Programming the Status Register System

Status Groups

Data Questionable Frequency Condition Register

The Data Questionable Frequency Condition Register continuously monitors the hardware and firmware

status of the signal generator; condition registers are read-only.

Data Questionable Frequency Transition Filters (negative and positive)

Specifies which types of bit state changes in the condition register set corresponding bits in the event

register. Changes can be positive (0 to 1) or negative (1 to 0).

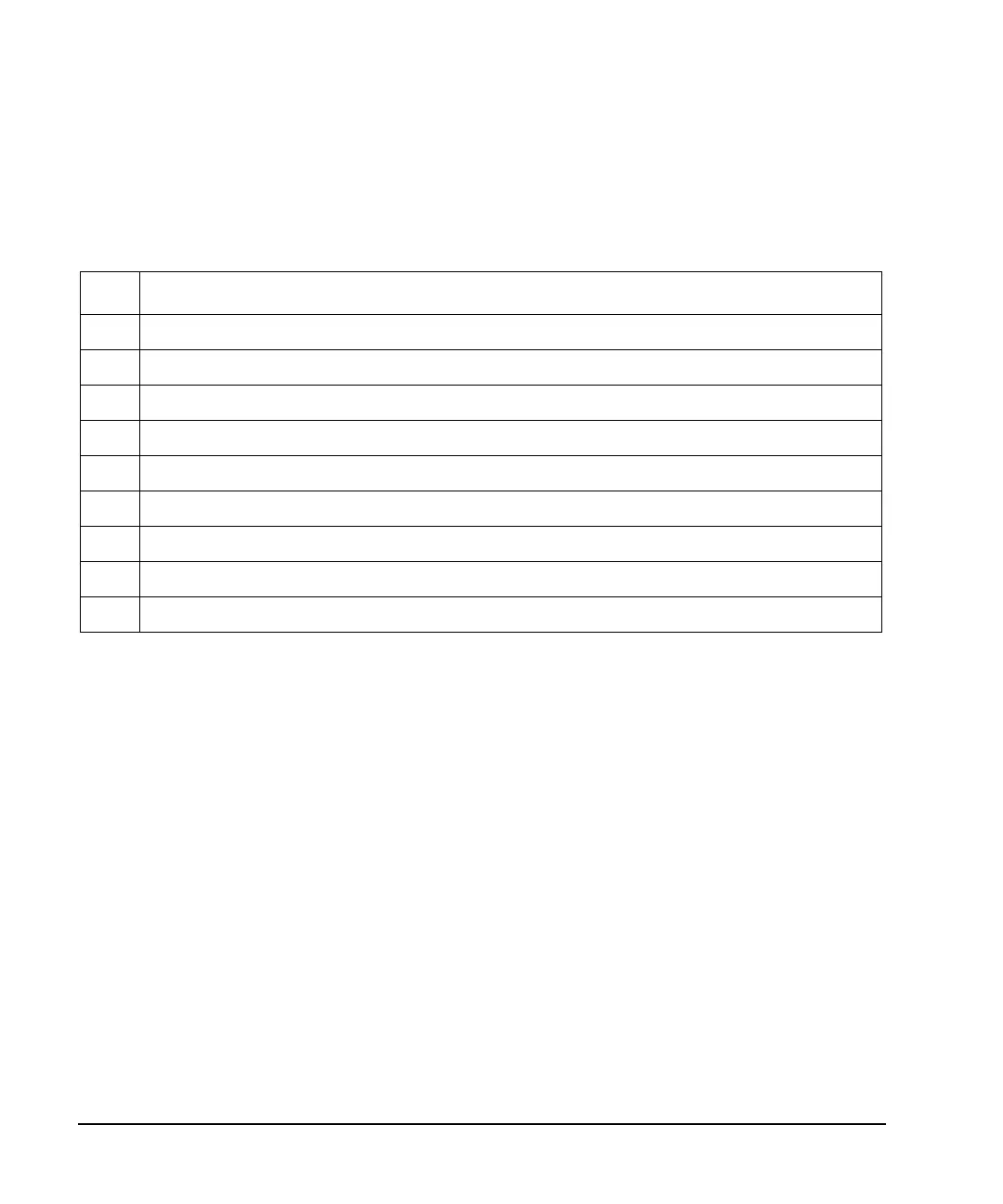

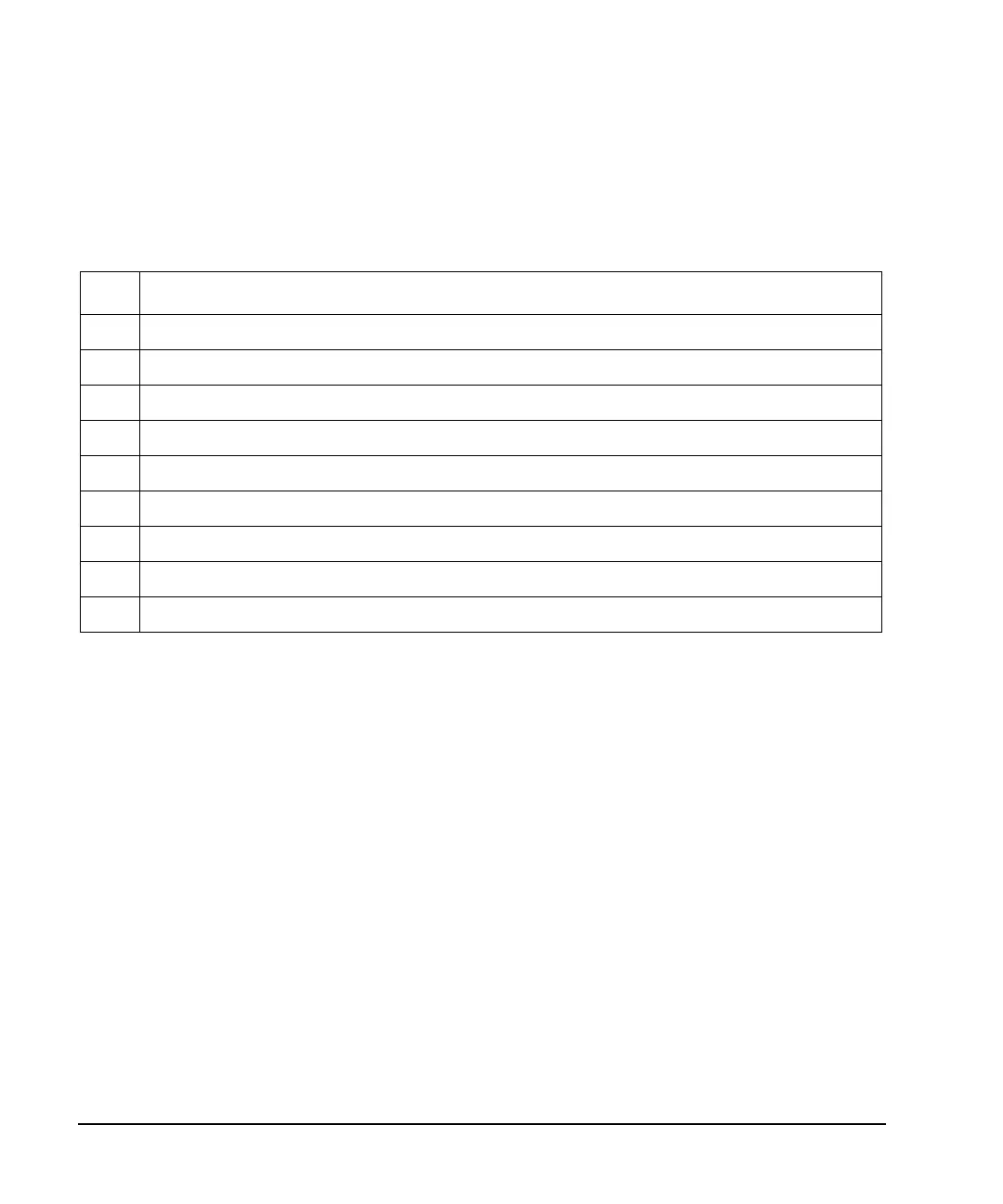

Table 3-9 Data Questionable Frequency Condition Register Bits

Bit Description

0 Synth. Unlocked. A 1 in this bit indicates that the synthesizer is unlocked.

1 10 MHz Ref Unlocked. A 1 in this bit indicates that the 10 MHz reference signal is unlocked.

2 1 Ghz Ref Unlocked. A 1 in this bit indicates that the 1 Ghz reference signal is unlocked.

3 Baseband 1 Unlocked. A 1 in this bit indicates that the baseband 1 generator is unlocked.

4 Unused. This bit is always set to 0.

5 Sampler Loop Unlocked. A 1 in this bit indicates that the sampler loop is unlocked.

6 YO Loop Unlocked. A 1 in this bit indicates that the YO loop is unlocked.

7−14 Unused. These bits are always set to 0.

15 Always 0.

Query: STATus:QUEStionable:FREQuency:CONDition?

Response: The decimal sum of the bits set to 1

Commands:

STATus:QUEStionable:FREQuency:NTRansition <value> (negative transition) or

STATus:QUEStionable:FREQuency:PTRansition <value> (positive transition)

where <value> is the sum of the decimal values of the bits you want to enable.

Queries:

STATus:QUEStionable:FREQuency:NTRansition?

STATus:QUEStionable:FREQuency:PTRansition?

Loading...

Loading...