AD9854

Rev. E | Page 14 of 52

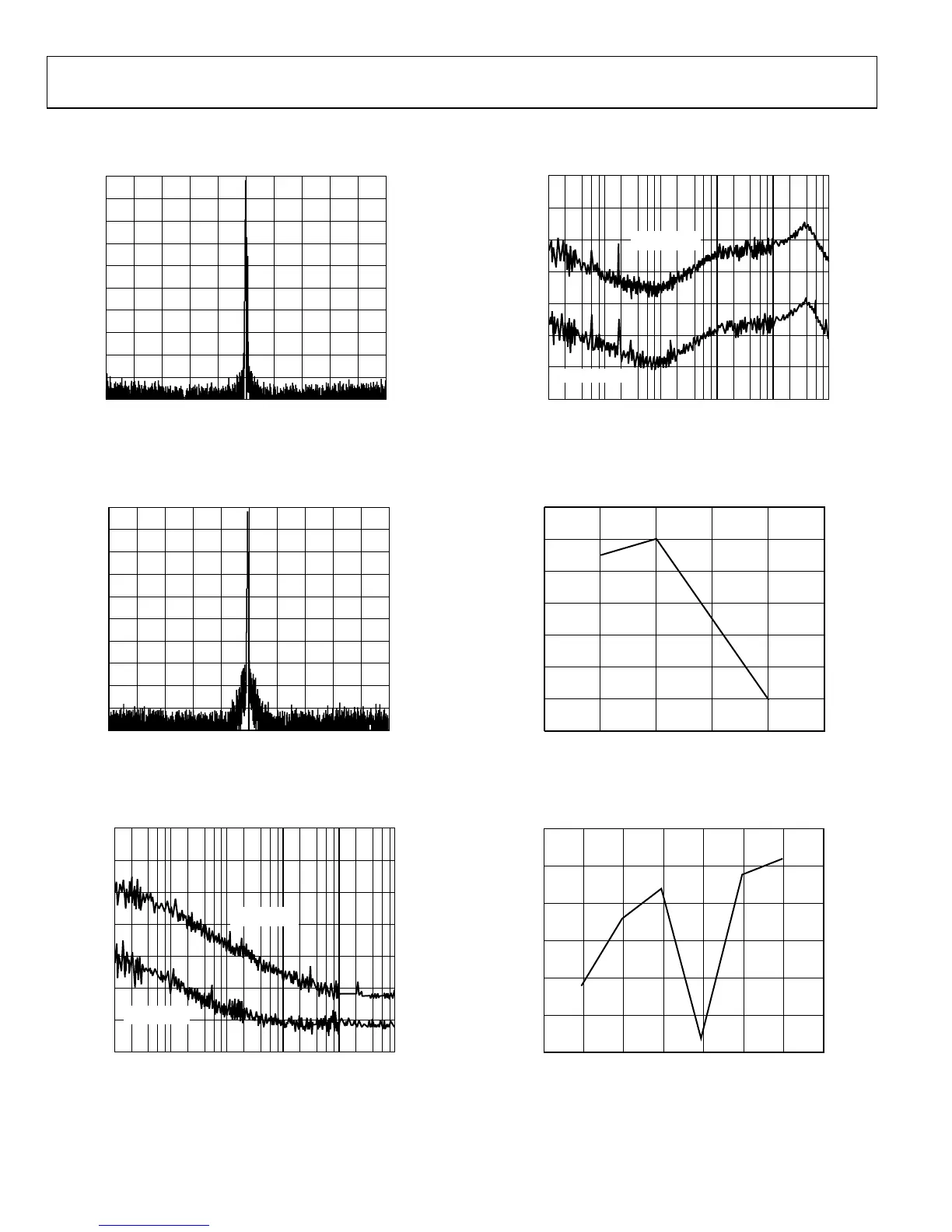

Figure 16 and Figure 17 show the narrow-band performance of the AD9854 when operating with a 200 MHz reference clock with the

REFCLK multiplier bypassed vs. a 20 MHz reference clock and the REFCLK multiplier enabled at 10×.

0

CENTER 39.1MHz

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

5kHz/ SPAN 50kHz

00636-016

Figure 16. Narrow-Band SFDR, 39.1 MHz, 50 kHz BW,

200 MHz REFCLK with REFCLK Multiplier Bypassed

0

CENTER 39.1MHz

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

5kHz/ SPAN 50kHz

00636-017

Figure 17. Narrow-Band SFDR, 39.1 MHz, 50 kHz BW,

20 MHz REFCLK with REFCLK Multiplier = 10×

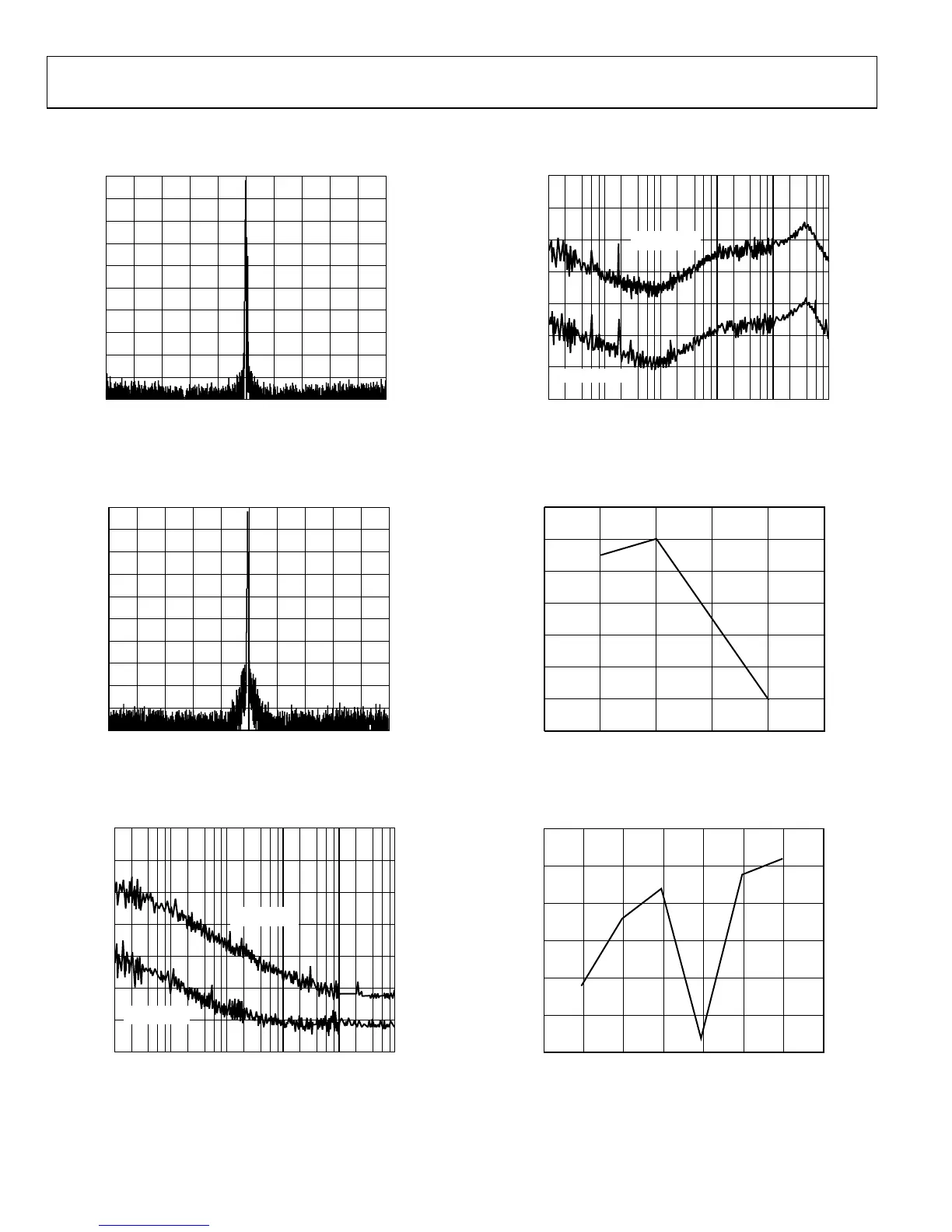

100

–110

–150

–120

–130

–140

–160

–170

PHASE NOISE (dBc/Hz)

A

OUT

= 80MHz

A

OUT

=5MHz

FREQUENCY (Hz)

10 1M100 100k10k1k

00636-018

Figure 18. Residual Phase Noise,

300 MHz REFCLK with REFCLK Multiplier Bypassed

FREQUENCY (Hz)

90

–100

–140

–110

–120

–130

–150

–160

10 1M100 100k10k1k

PHASE NOISE (dBc/Hz)

A

OUT

=80MHz

A

OUT

=5MHz

00636-019

Figure 19. Residual Phase Noise,

30 MHz REFCLK with REFCLK Multiplier = 10×

DAC CURRENT (mA)

55

0 5 10 15 20 25

SFDR (dBc)

54

53

52

51

50

49

48

00636-020

Figure 20. SFDR vs. DAC Current, 59.1 A

OUT

,

300 MHz REFCLK with REFCLK Multiplier Bypassed

FREQUENCY (MHz)

620

0

SUPPLY CURRENT (mA)

615

610

605

600

595

590

20 40 60 80 100 120 140

00636-021

Figure 21. Supply Current vs. Output Frequency (Variation Is Minimal,

Expressed as a Percentage, and Heavily Dependent on Tuning Word)

Loading...

Loading...