AD9854

Rev. E | Page 18 of 52

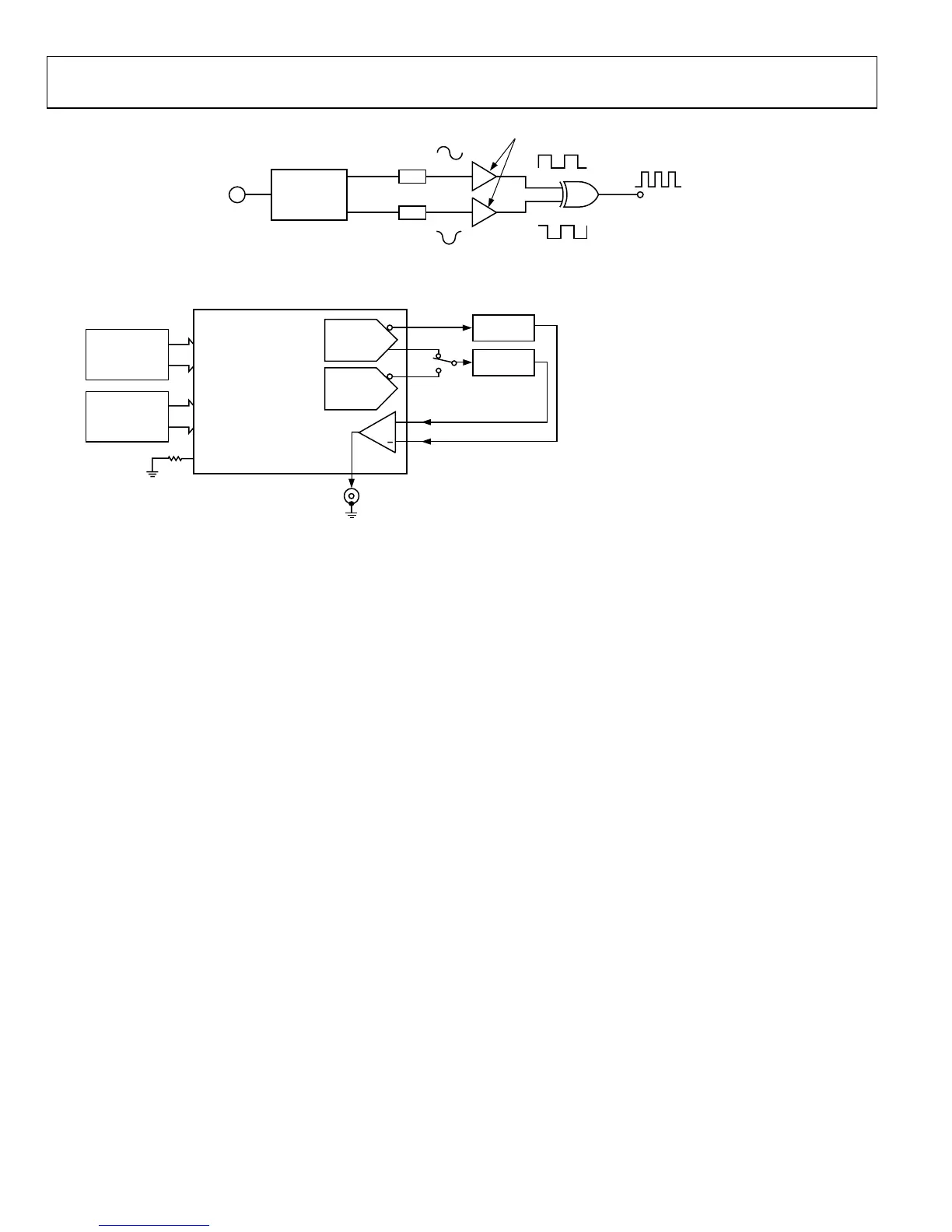

CLOCK OUT = 200MHz

LPF

SIN

LPF

AD9854

COS

REFERENCE

CLOCK

COMP

R

TORS

A

OUT

= 100MHz

00636-033

Figure 33. Clock Frequency Doubler

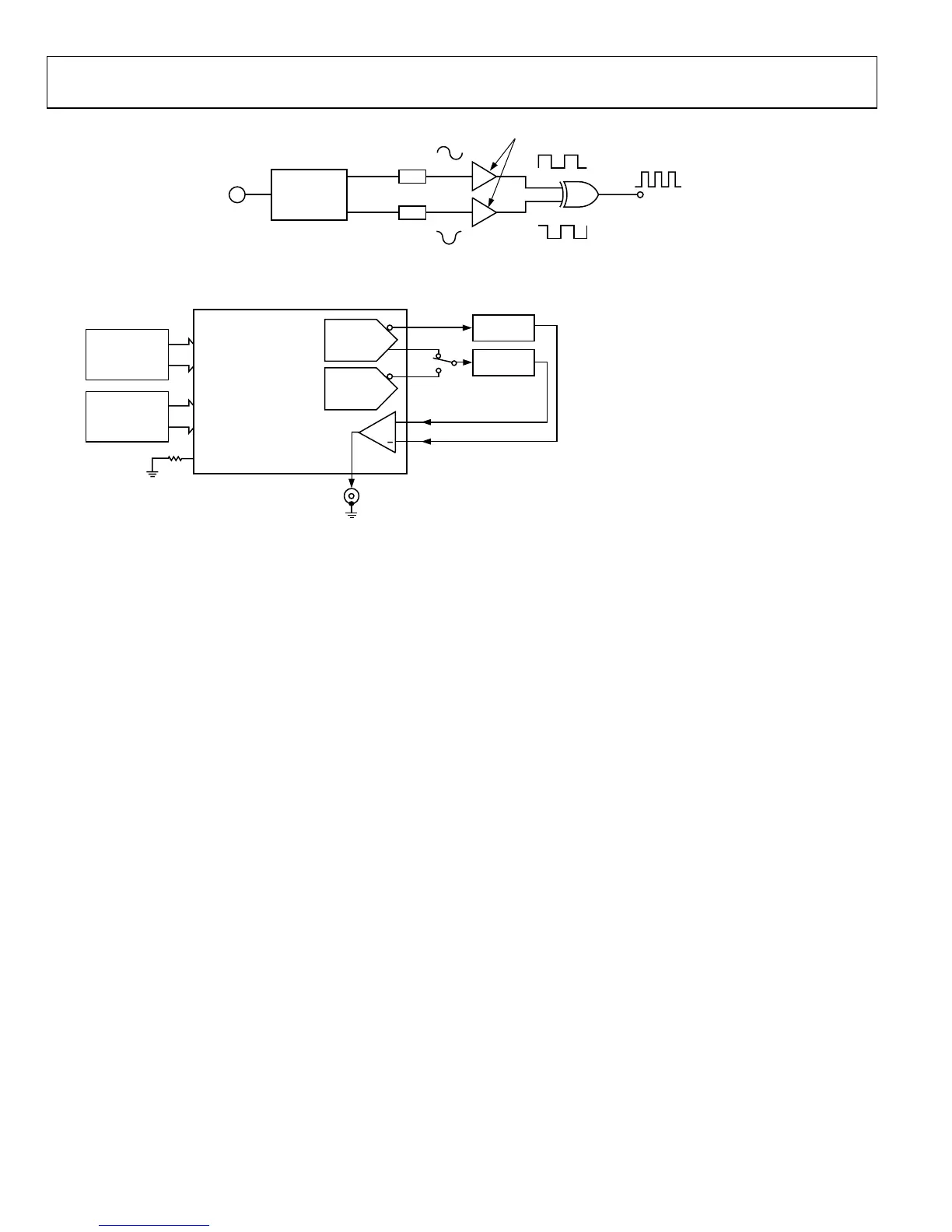

µPROCESSOR/

CONTROLLER

FPGA, ETC.

R

SET

8-BIT PARALLEL OR

SERIAL PROGRAMMING

DATA AND CONTROL

SIGNALS

AD9854

+

REFERENCE

CLOCK

300MHz MAX DIRECT

MODE OR 15MHz TO 75MHz

MAX IN THE 4× TO 20×

CLOCK

MULTIPLIER MODE

2kΩ

I DAC

1

2

Q DAC OR

CONTROL

DAC

LOW-PASS

FILTER

LOW-PASS

FILTER

00636-034

NOTES

1. I

OUT

= APPROX 20mA MAX WHEN R

SET

= 2kΩ.

2. SWITCH POSITION 1 PROVIDES COMPLEMENTARY

SINUSOIDAL SIGNALS TO THE COMPARATOR

TO PRODUCE A FIXED 50% DUTY CYCLE FROM THE

COMPARATOR.

3. SWITCH POSITION 2 PROVIDES THE SAME DUTY CYCLE

USING QUADRATURE SINUSOIDAL SIGNALS TO THE

COMPARATOR OR A DC THRESHOLD VOLTAGE TO

ALLOW SETTING OF THE COMPARATOR DUTY CYCLE

(DEPENDS ON THE CONFIGURATION OF THE Q DAC).

CMOS LOGIC CLOCK OUT

Figure 34. Frequency Agile Clock Generator Applications for the AD9854

Loading...

Loading...