AD9854

Rev. E | Page 33 of 52

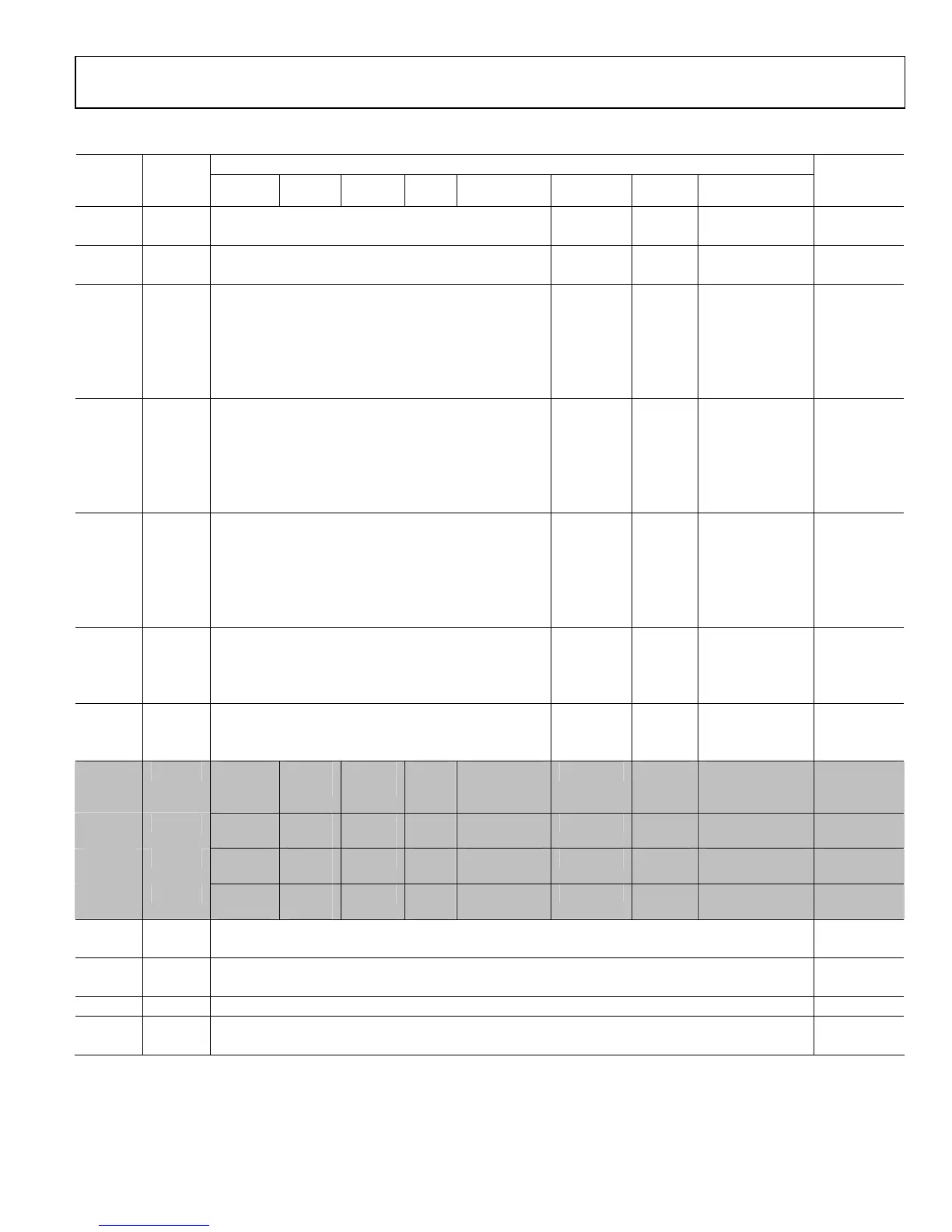

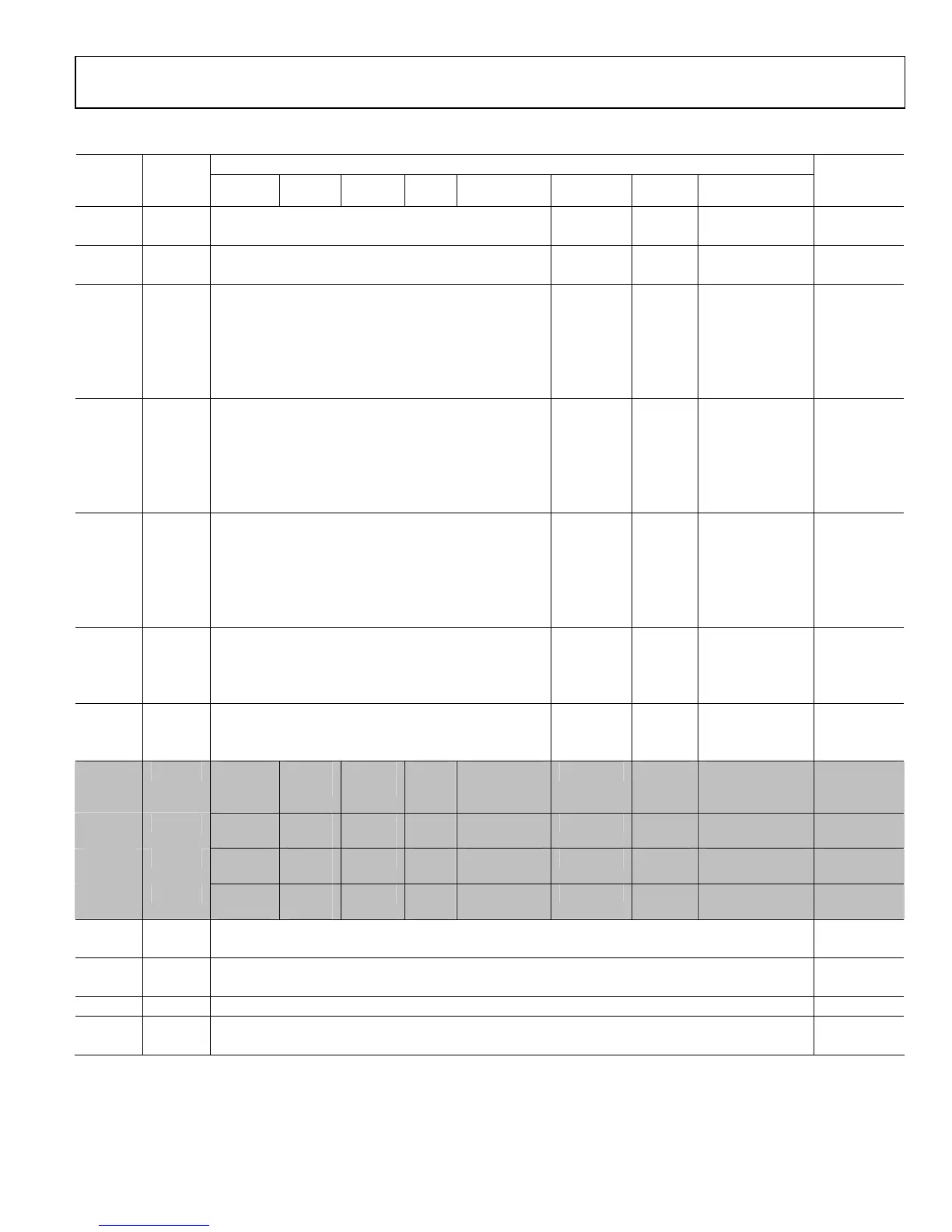

Table 8. Register Layout

1

AD9854 Register Layout Parallel

Address

(Hex)

Serial

Address

(Hex)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Default

Value

(Hex)

00 0 Phase Adjust Register 1 <13:8> (Bits 15, 14, don’t care) Phase 1 00

01 Phase Adjust Register 1 <7:0> 00

02 1 Phase Adjust Register 2 <13:8> (Bits 15, 14, don’t care) Phase 2 00

03 Phase Adjust Register 2 <7:0> 00

04 2 Frequency Tuning Word 1 <47:40> Freq 1 00

05 Frequency Tuning Word 1 <39:32> 00

06 Frequency Tuning Word 1 <31:24> 00

07 Frequency Tuning Word 1 <23:16> 00

08 Frequency Tuning Word 1 <15:8> 00

09 Frequency Tuning Word 1 <7:0> 00

0A 3 Frequency Tuning Word 2 <47:40>

0B Frequency Tuning Word 2 <39:32> 00

0C Frequency Tuning Word 2 <31:24> 00

0D Frequency Tuning Word 2 <23:16> 00

0E Frequency Tuning Word 2 <15:8> 00

0F Frequency Tuning Word 2 <7:0> 00

10 4 Delta frequency word <47:40> 00

11 Delta frequency word <39:32> 00

12 Delta frequency word <31:24> 00

13 Delta frequency word <23:16> 00

14 Delta frequency word <15:8> 00

15 Delta frequency word <7:0> 00

16 5 Update clock <31:24> 00

17 Update clock <23:16> 00

18 Update clock <15:8> 00

19 Update clock <7:0> 40

1A 6 Ramp rate clock <19:16> (Bits 23, 22, 21, 20, don’t care) 00

1B Ramp rate clock <15:8> 00

1C Ramp rate clock <7:0> 00

1D 7

Don’t

care

CR [31]

Don’t

care

Don’t

care

Comp

PD

Reserved,

always low

QDAC PD DAC PD DIG PD 10

1E

Don’t

care

PLL

range

Bypass

PLL

Ref

Mult 4

Ref Mult 3 Ref Mult 2

Ref

Mult 1

Ref Mult 0 64

1F

CLR

ACC 1

CLR

ACC 2

Triangle

SRC

QDAC

Mode 2 Mode 1 Mode 0

Internal/external

update clock

01

20

Don’t

care

Bypass

inv sinc

OSK EN

OSK

INT

Don’t care Don’t care LSB first SDO active CR [0] 20

21 8 Output shaped keying I multiplier <11:8> (Bits 15, 14, 13, 12 don’t care) 00

22 Output shaped keying I multiplier <7:0> 00

23 9 Output shaped keying Q multiplier <11:8> (Bits 15, 14, 13, 12 don’t care) 00

24 Output shaped keying Q multiplier <7:0> 00

25 A Output shaped keying ramp rate <7:0> 80

26 B QDAC <11:8> (Bits 15, 14, 13, 12 don’t care) 00

27 QDAC <7:0> (data is required to be in twos complement format)

1

The shaded sections comprise the control register.

Loading...

Loading...