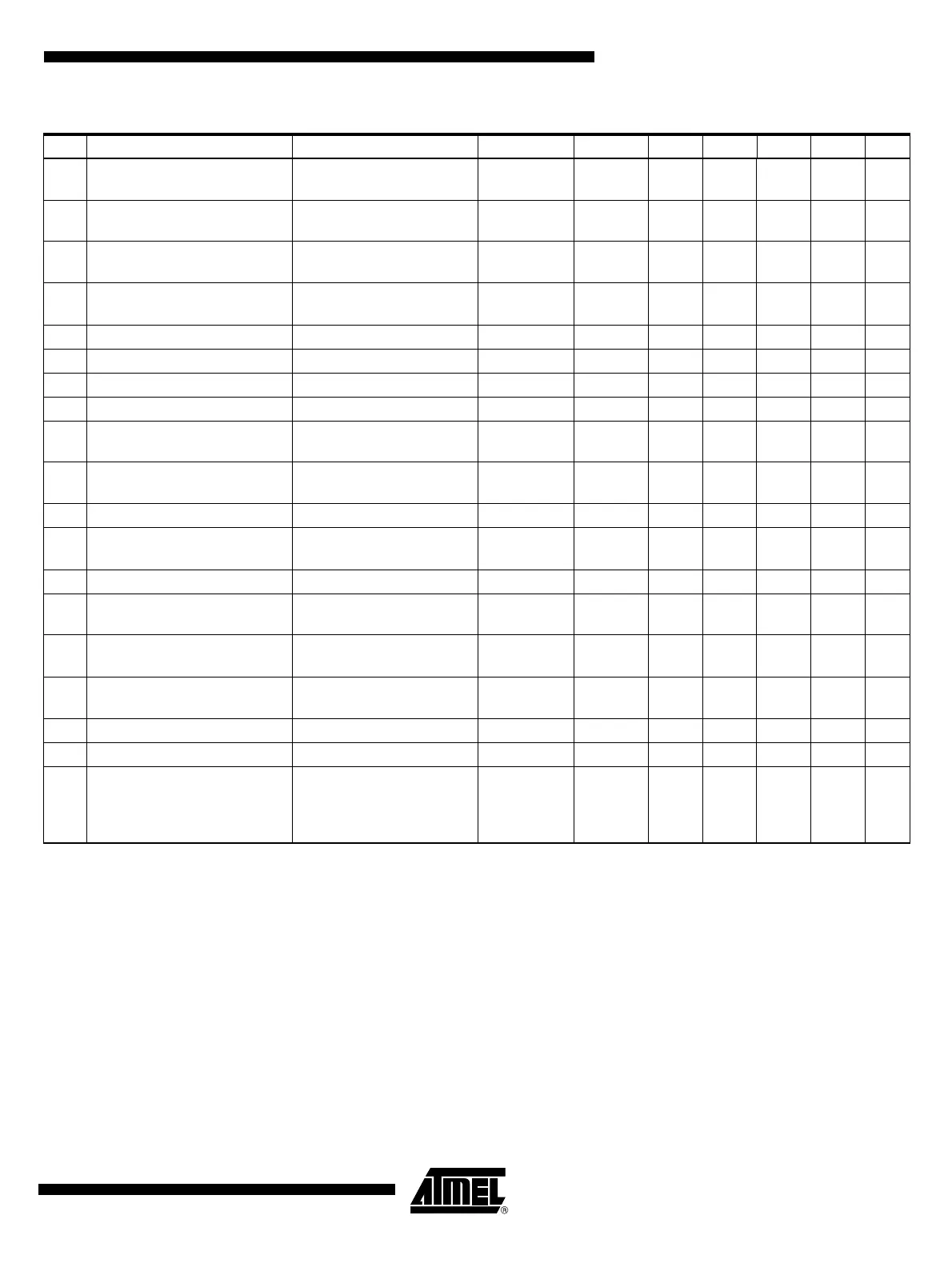

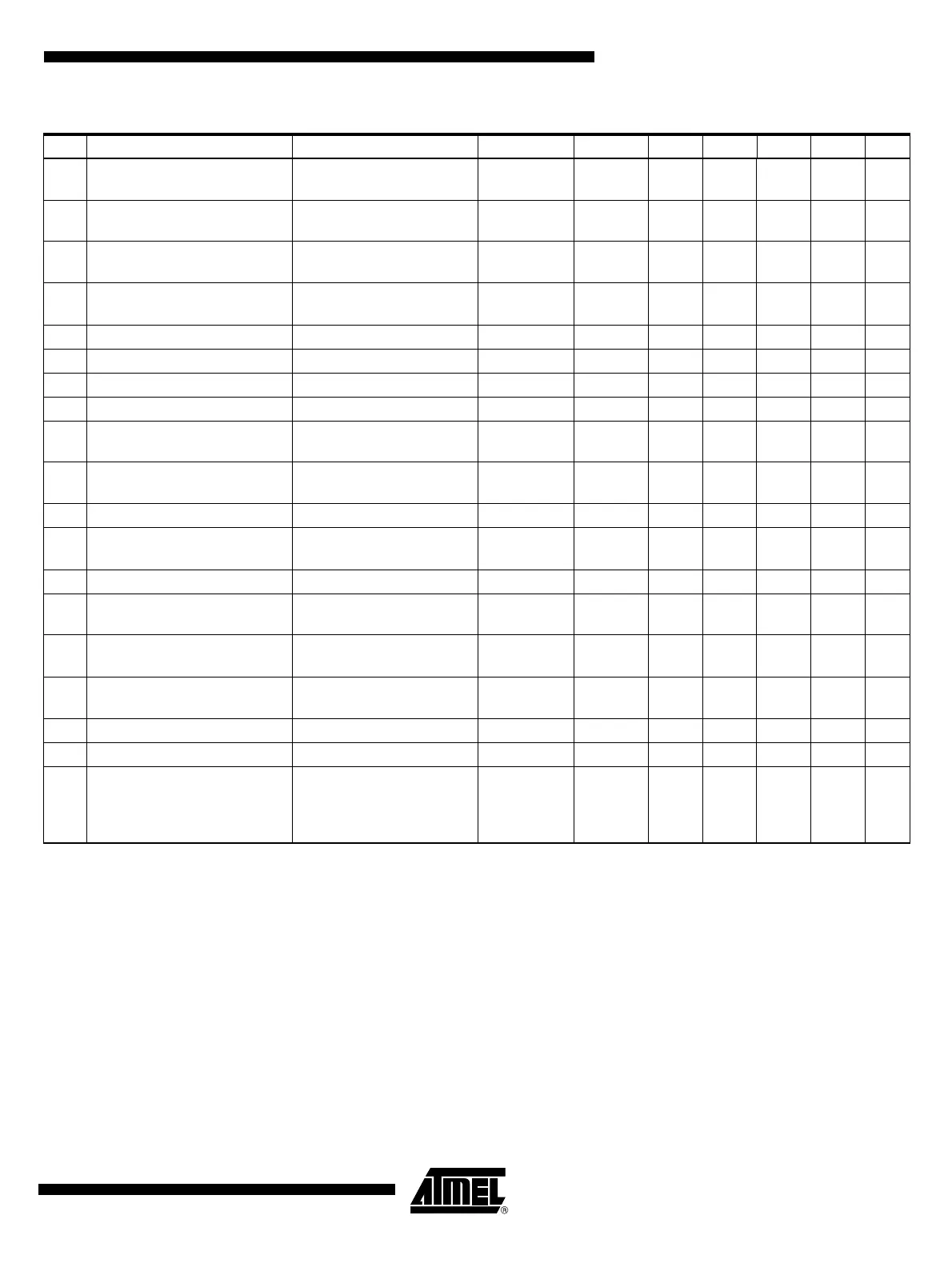

69

4929B–AUTO–01/07

ATA6264 [Preliminary]

21.7

Time from SSQ falling edge to

MISO MSB valid

(2)

MISO t

MISOMSB_V

0 400 ns A

21.8

Time from SCLK rising edge to

MISO valid

(2)

MISO t

MISOV

040nsA

21.9

Time from SSQ rising edge to

MISO tristate condition

(2)

MISO t

MISOhiZ

040nsA

21.10

No-data time between serial

interface commands

t

nodata

1.5 µs A

(3)

21.11 Clock frequency CLK f

SCLK

08MHzA

(3)

21.12 Pull-up current VPERI SSQ R

pu_SSQ

–95 –45 µA A

21.13 Pull-up current VPERI SCLK R

pu_SCLK

–95 –45 µA A

21.14 SCLK high/low time SCLK t

CL

40 ns A

(3)

21.15 Input voltage high level

SSQ, SCLK,

MOSI

V

H

0.5 ×

V

VPERI

A

21.16 Input voltage low level

SSQ, SCLK,

MOSI

V

L

0.25 ×

V

VPERI

A

21.17 Input voltage hysteresis SCLK V

HYS

50 250 mV A

21.18 Output voltage high level I

MISO

= –1 mA to 0 mA MISO V

H

V

VPERI

– 0.8

V

VPERI

VA

21.19 Output voltage low level I

MISO

= 0 mA to 1 mA MISO V

L

00.4VA

21.20

Output current high level driven

to short circuit

V

VPERI

= 5V MISO I

MISO

–47 –10 mA A

21.21

Output current low level sinking

from VPERI level

V

VPERI

= 5V MISO I

MISO

645mAA

21.22 Input capacitance

SSQ, SCLK,

MOSI

C

IN

10 pF D

21.23 Output capacitance Switched-off condition MISO C

MISO

10 pF D

21.24 Leakage current Switched-off condition MISO I

MISO

–10 +10 µA A

21.25

Number of clock cycles to be

detected between falling and

rising edge of SSQ, to set error

signal in status register to “0”

16 16 A

Table 22-1. Electrical Characteristics (Continued)– Serial Interface Commands

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. Voltage levels for serial interface timing measurements: High level = 0.7 × V

VPERI

, low level = 0.2 × V

VPERI

2. Timing specified with a 100-pF external load at pin MISO

3. System requirement

Loading...

Loading...