— 12 —

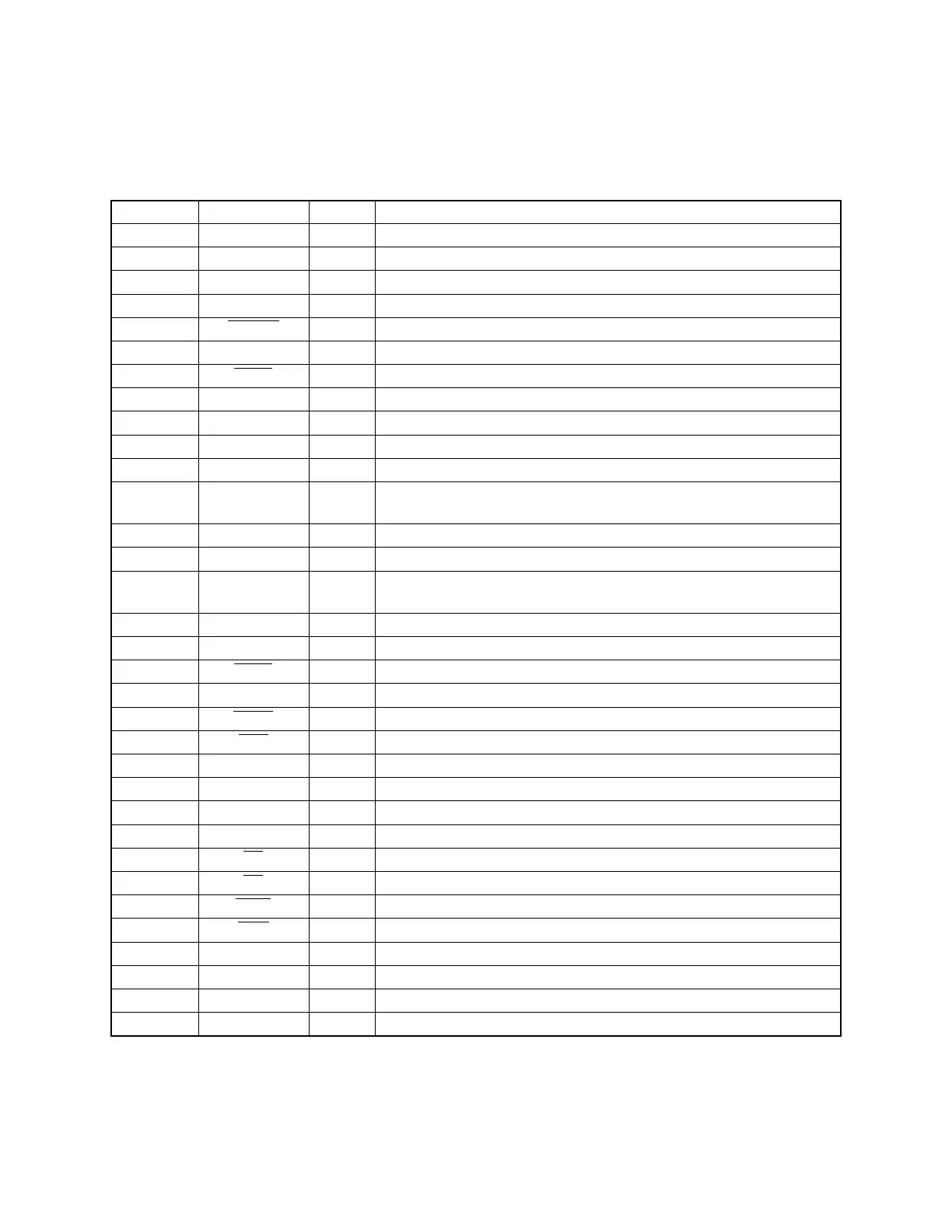

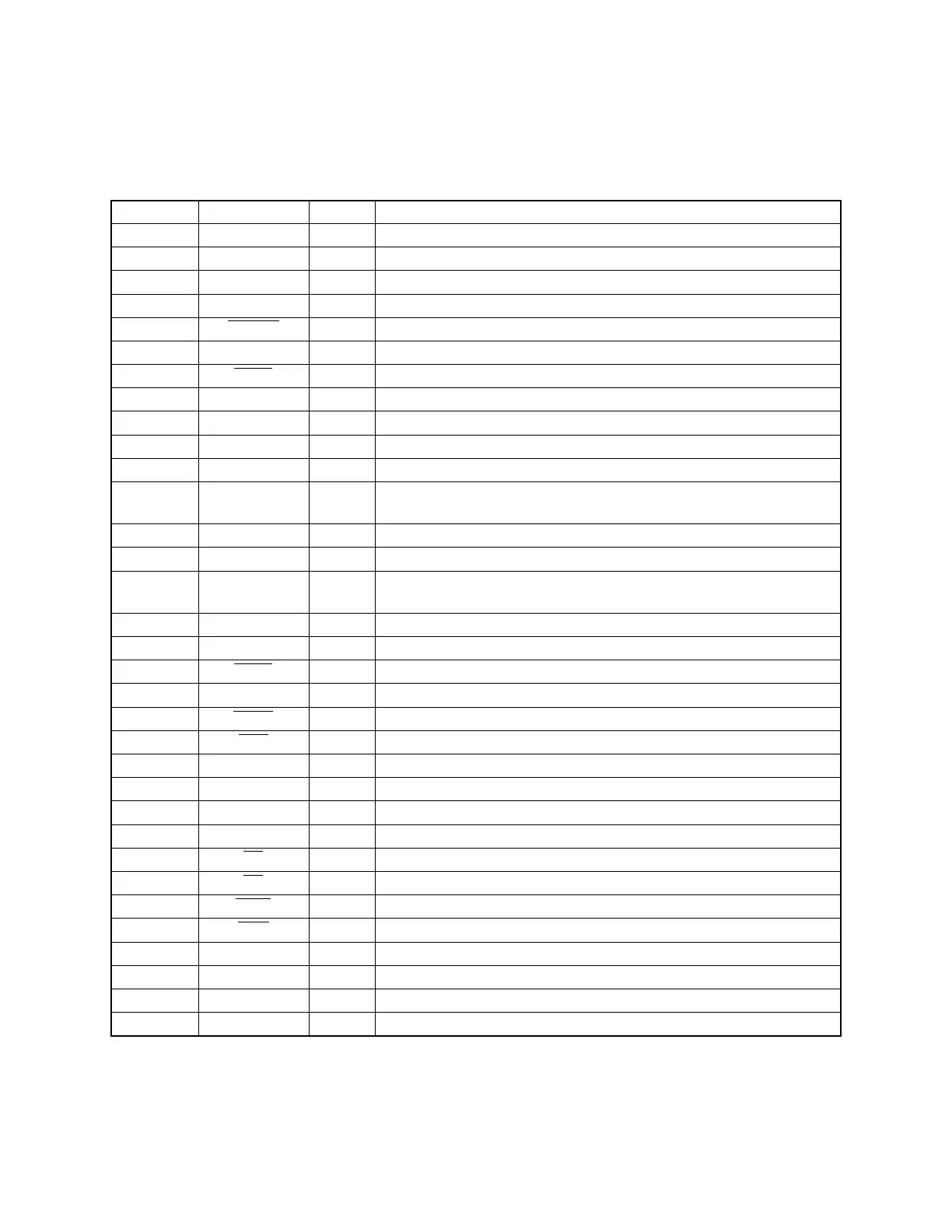

Pin No. Terminal In/Out Function

1 VCC In VCC (5 V) source.

2 ~ 5 PB0 ~ PB3 Out Data bus for LCD driver.

6 PB4 Out Chip enable signal for LCD driver.

7 PB5 Out Read/write signal for LCD driver.

8 DREQ0 — DMA (Direct Memory Access) request.

9 PB7 Out Register selection signal for LCD driver.

10 RES0 In Not used.

11 VSS In Ground terminal (0 V).

12 TXD0 Out MIDI signal output.

13, 15 ~ 17 P91, P93~P95 In Key input signal from buttons.

14 RXD0 In MIDI signal input.

18 ~ 21

D0 ~ D15 In/Out Data bus.

23 ~ 34

22 VSS In Ground terminal (0 V).

35 VCC In Vcc (5 V) source.

36 ~ 43,

A0 ~ A19 Out Address bus.

45 ~ 56

44, 57 VSS In Ground terminal (0 V).

55, 59, 60 P52, P61, P62 In Key input signal from buttons.

58 WAIT — Not used.

61 CLKOUT Out Clock signal (16 MHz).

62 STBY — Not used.

63 RES In Reset signal at VDD (5 V) supplied.

64 NMI In Power ON signal input.

65 VSS In Ground terminal (0 V).

66, 67 EXTAL, XTAL In Clock (16 MHz) input.

68 VCC In Vcc (5 V) source.

69 AS — Not used.

70 RD Out Read signal.

71 HWR Out Write signal for upper data bus.

72 LWR Out Write signal for lower data bus.

73 ~ 75 MD0 ~ MD2 In Mode selection terminals.

76, 77 AVCC, VREF In Power source and reference voltage for internal A/D, D/A.

78 AN0 In Battery voltage detection (Not used).

79 AN1 In Pitch bender voltage detection.

CPU (LSI9: HD6433042SB51F)

The 16 bit CPU contains a 512K-bit ROM, a 16K-bit RAM, eleven 8-bit I/O ports, an A/D converter and serial

interfaces. The CPU accesses to the RAM1, RAM2, DSP, Key controller, FDD controller and LCD driver

LSI. The CPU also controls buttons, LEDs, bender input and MIDI input/output.

Loading...

Loading...