5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

6-22-24R00-1B9

6-22-24R00-1BA

32.768KHZ

6-22-32R76-0B2

6-22-32R76-0BJ

RTC (10M OHM RES): DO NOT CHANGE TO 0402

GLAN

WLAN

SSD (x4 LANE)

PEG (x8)

PCIE CLK

Usage

100 MHz 100 MHz

5

6

9

10

SRCCLKREQ#

5

6

9

10

˓

˓˓

˓

Any used, enable, and mapped SRCCLKREQ# signal

should connect to a PCIE* connector pin or

a device down ball with 10K ohm external pull-up resistor to core rail.

˓

˓˓

˓

SRCCLKREQ#[7:0] signal can be mapped to any of the CLKOUT_PCIE_P/N[7:0]

˓

˓˓

˓

SRCCLKREQ#[15:8] signal can be mapped to any of the CLKOUT_PCIE_P/N[15:8]

ὅ

ὅὅ

ὅ䄏

䄏䄏

䄏

intel

姕

姕姕

姕妰

妰妰

妰炻

炻炻

炻

GPIO power rail PU SUS well

Ữ

ỮỮ

Ữ

SRCCLKREQ#

⌣

⌣⌣

⌣

PU core rail

㓭

㓭㓭

㓭忚

忚忚

忚ℍ

ℍℍ

ℍ

S3

㚱

㚱㚱

㚱⎗

⎗⎗

⎗傥

傥傥

傥忈

忈忈

忈ㆸ

ㆸㆸ

ㆸ㺷

㺷㺷

㺷暣

暣暣

暣

D02 0707

D02 0714

D02 0714

XCLK_RBIAS

PCH_XDP_CLK_DN

PCH_XDP_CLK_DP

RTC_X2

RTC_X1

LAN_CLKREQ#

PEG_CLKREQ#

PEG_CLKREQ#

WLAN_CLKREQ#

SSD_CLKREQ#

PEG_CLKREQ#

LAN_CLKREQ#

VDD1.0

3.3VS

PCH_CPU_PCIBCLK_R_DP [5]

PCH_CPU_PCIBCLK_R_DN [5]

PCH_CPU_BCLK_R_DP[5]

PCH_CPU_BCLK_R_DN[5]

CPU_24MHZ_R_DP[5]

CPU_24MHZ_R_DN[5]

SSD_CLKREQ#[33]

LAN_CLKREQ#[35]

VDD1.0[29,43,44]

3.3VS[9,10,11,12,13,14,23,25,26,27,29,30,32,33,35,36,37,38,39,40,43,45,47,49]

CLK_PCIE_GLAN# [35]

CLK_PCIE_GLAN [35]

CLK_PCIE_MINI [32]

CLK _PCIE _MIN I# [ 32]

CLK_PCIE_SSD [33]

CLK_PCIE_SSD# [33]

VGA_PEXCLK# [18]

VGA_PEXCLK [18]

PEG_CLKREQ#[18]

WLAN_CLKREQ#[32]

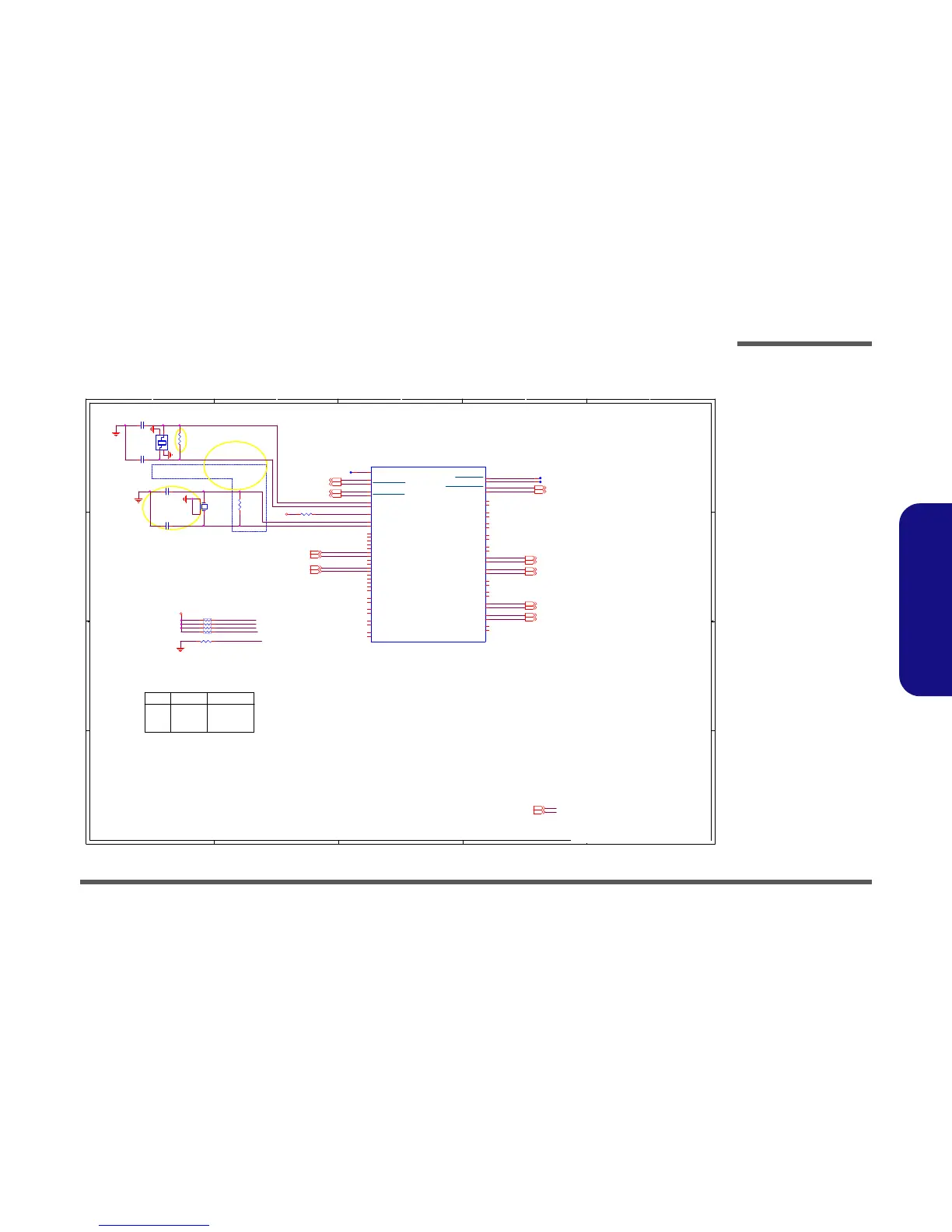

Title

Size Document Number Rev

Date: S heet

of

6-71-N15R0-D02A

2.0A

[28] PCH 7/12-CLKOUT

A3

28 62Tuesday, August 18, 2015

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

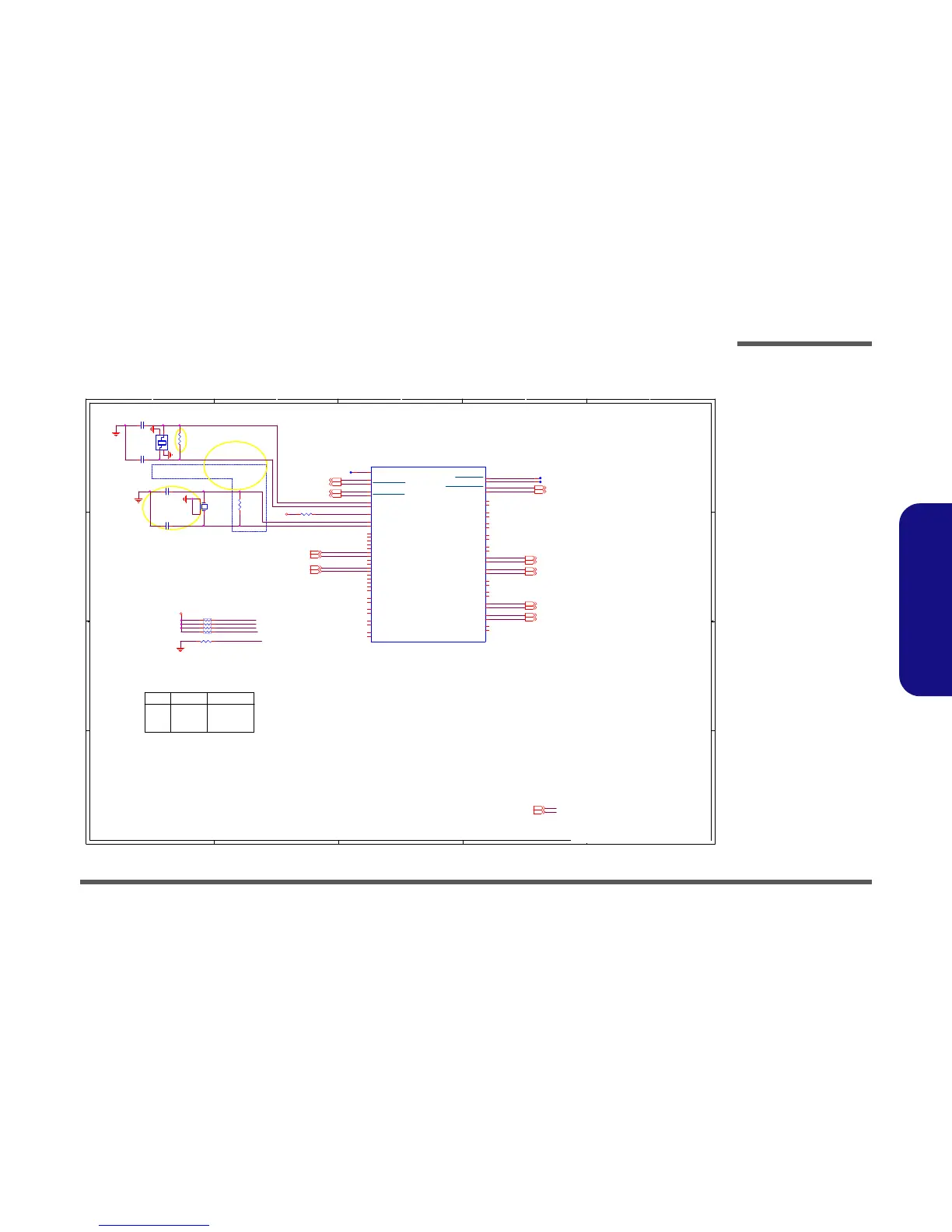

Title

Size Document Number Rev

Date: S heet

of

6-71-N15R0-D02A

2.0A

[28] PCH 7/12-CLKOUT

A3

28 62Tuesday, August 18, 2015

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number Rev

Date: S heet

of

6-71-N15R0-D02A

2.0A

[28] PCH 7/12-CLKOUT

A3

28 62Tuesday, August 18, 2015

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

R1765

10M_06

C1389

1.5p_50V_04

SPT-H_PCH

7 OF 12 REV = 1.3

U138G

HM170

GPP_A16/CLKOUT_48

AR17

CLKOUT_CPUNSSC_P

G1

CLKOUT_CPUNSSC

F1

CLKOUT_CPUBCLK_P

G2

CLKOUT_CPUBCLK

H2

XTAL24_OUT

A5

XTAL24_IN

A6

XCLK_BIASREF

E1

RTCX1

BC9

RTCX2

BD10

GPP_B5/SRCCLKREQ0#

BC24

GPP_B6/SRCCLKREQ1#

AW24

GPP_B7/SRCCLKREQ2#

AT24

GPP_B8/SRCCLKREQ3#

BD25

GPP_B9/SRCCLKREQ4#

BB24

GPP_B10/SRCCLKREQ5#

BE25

GPP_H0/SRCCLKREQ6#

AT33

GPP_H1/SRCCLKREQ7#

AR31

GPP_H2/SRCCLKREQ8#

BD32

GPP_H3/SRCCLKREQ9#

BC32

GPP_H4/SRCCLKREQ10#

BB31

GPP_H5/SRCCLKREQ11#

BC33

GPP_H6/SRCCLKREQ12#

BA33

GPP_H7/SRCCLKREQ13#

AW33

GPP_H8/SRCCLKREQ14#

BB33

GPP_H9/SRCCLKREQ15#

BD33

CLKOUT_PCIE_N15

R13

CLKOUT_PCIE_P15

R11

CLKOUT_PCIE_N14

P1

CLKOUT_PCIE_P14

R2

CLKOUT_PCIE_N13

W7

CLKOUT_PCIE_P13

Y5

CLKOUT_PCIE_N12

U2

CLKOUT_PCIE_P12

U3

CLKOUT_ITPXDP

L1

CLKOUT_ITPXDP_P

L2

CLKOUT_CPUPCIBCLK

J1

CLKOUT_CPUPCIBCLK_P

J2

CLKOUT_PCIE_N0

N7

CLKOUT_PCIE_P0

N8

CLKOUT_PCIE_N1

L7

CLKOUT_PCIE_P1

L5

CLKOUT_PCIE_N2

D3

CLKOUT_PCIE_P2

F2

CLKOUT_PCIE_N3

E5

CLKOUT_PCIE_P3

G4

CLKOUT_PCIE_N4

D5

CLKOUT_PCIE_P4

E6

CLKOUT_PCIE_N5

D8

CLKOUT_PCIE_P5

D7

CLKOUT_PCIE_N6

R8

CLKOUT_PCIE_P6

R7

CLKOUT_PCIE_N7

U5

CLKOUT_PCIE_P7

U7

CLKOUT_PCIE_N8

W10

CLKOUT_PCIE_P8

W11

CLKOUT_PCIE_N9

N3

CLKOUT_PCIE_P9

N2

CLKOUT_PCIE_N10

P3

CLKOUT_PCIE_P10

P2

CLKOUT_PCIE_N11

R3

CLKOUT_PCIE_P11

R4

C1391 1.5p_50V_04

C1390

22p_50V_NPO_04

X5

1TJS125DJ4A420P

CM200S

14

3 2

X6

FSX3M_24MHZ

FSX3M

21

34

R1760

1M_1%_04

C1392

22p_50V_NPO_04

RN7

10K_8P4R_04

1

2

3

4 5

6

7

8

R1764 2.7K_1%_04

R1761 *10K_04

Loading...

Loading...