A

NO REBOOThis signal has an integrated weak

pull-down resistor (20 KΩ nominal) to

disable the no reboot strap functionality

by default.

To enable no reboot on TCO Timer

expiration, this signal should be

pulled-up to V3.3S through a 1k to 2.2 KΩ

±5% resistor.

BOOT STARP

This signal has an integrated weak

pull-down resistor (20 KΩ nominal)

to default boot from SPI.

To enable boot to LPC, this signal

should be pulled up to V3.3S through

a 1k to 2.2 KΩ ±5% resistor.

嶇

BIOS

䡢

娵

嶇

BIOS

䡢

娵

DEBUG

TX -> D+

RX -> D-

嶇

BIOS

䡢

娵

GPIO

H: W / TPM

L: W/O TPM

Differential between RCOMPN/RCOMPP.

Length matched to less than 1% trace.

DEL ASM_SMI#

XTAL SELECT-1

HIGH -> 24 MHZ

LOW -> 38.4 MHZ

M.2 CNVI STRAP

HIGH -> DISABLE

LOW -> ENABLE

Leakage

D01A for CNVI samuel

D01A for CNVI samuel

Raven add 0731

D02_102518_Alex_Typec DP issue

D02_1109_Alex

3.3VS

3.3VA

3.3VS

3.3VS

3.3VS

PCH1.8VA

PCH1.8VA

PCH1.8VA

3.3VS

PCH1.8VA PCH1.8VA

3.3VS8,9,23,24,27,28,29,30,31,32,33,34,35,39,40,42,43,44,45,47,48,52,59,70,71

VDD34,23,30,31,33,36,39,40,42,44,45,46,47,48,49,52,53,55,56,57,58,59,60,63,70,71,72

CPU_2_PCH_TRIGGER 6

PCH_2_CPU_TRIGGER 6

SB_BLON 28

3.3VA4,30,31,32,33,36,44,48,53

SATA_PWR_EN 43

CNVI_MFUART2_RXD40

CNVI_GNSS_PA_BLANKING40

CNVI_WGR_CLKP 40

CNVI_WGR_CLKN 40

CNVI_WGR_D0N 40

CNVI_WGR_D0P 40

CNVI_WGR_D1N 40

CNVI_WGR_D1P 40

CNVI_WT_CLKN 40

CNVI_WT_CLKP 40

CNVI_WT_D0N 40

CNVI_WT_D0P 40

CNVI_WT_D1N 40

CNVI_WT_D1P 40

CNVI_BRI_DT40

CNVI_RGI_DT40

CNVI_MFUART2_TXD40

H_SKTOCC_N4,34

PCH1.8VA36

GPP_J148,53

H_TRST# 4

H_PREQ# 4

H_PRDY# 4

GPIO4_1V8_MAIN_EN_R24

CNVI_BRI_RSP40

CNVI_RGI_RSP40

SMD_741169

SMC_741169

I2C_SCL_TP43

I2C_SDA_TP43

I2C2_SDA56,59

I2C2_SCL56,59

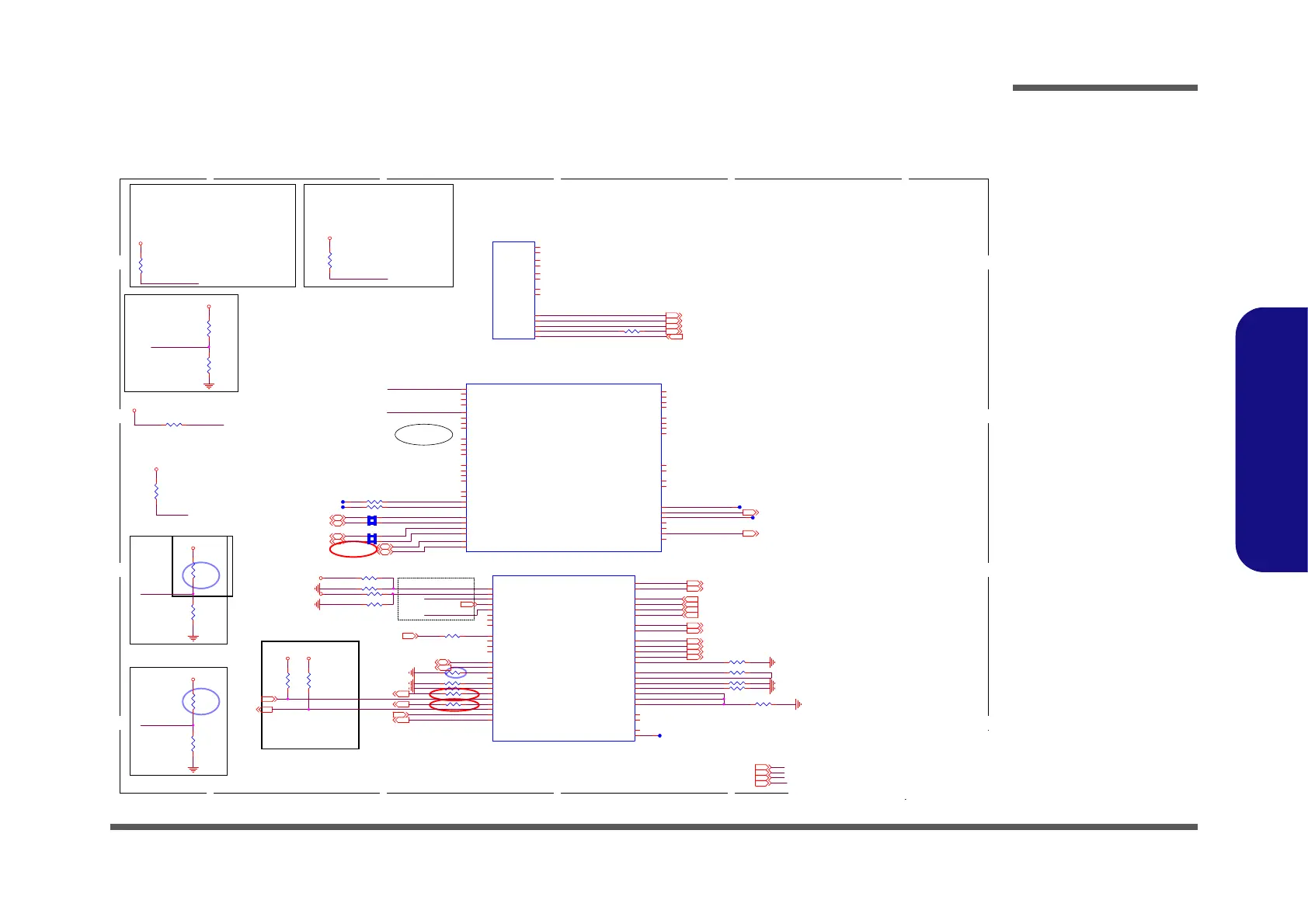

Title

Size Document Number Rev

Date: Sheet

of

6-71-NH5D0-D02

D02

[38] PCH 10_11/12-UART/I2C/GPIO

A3

38 74Friday, February 07, 2020

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

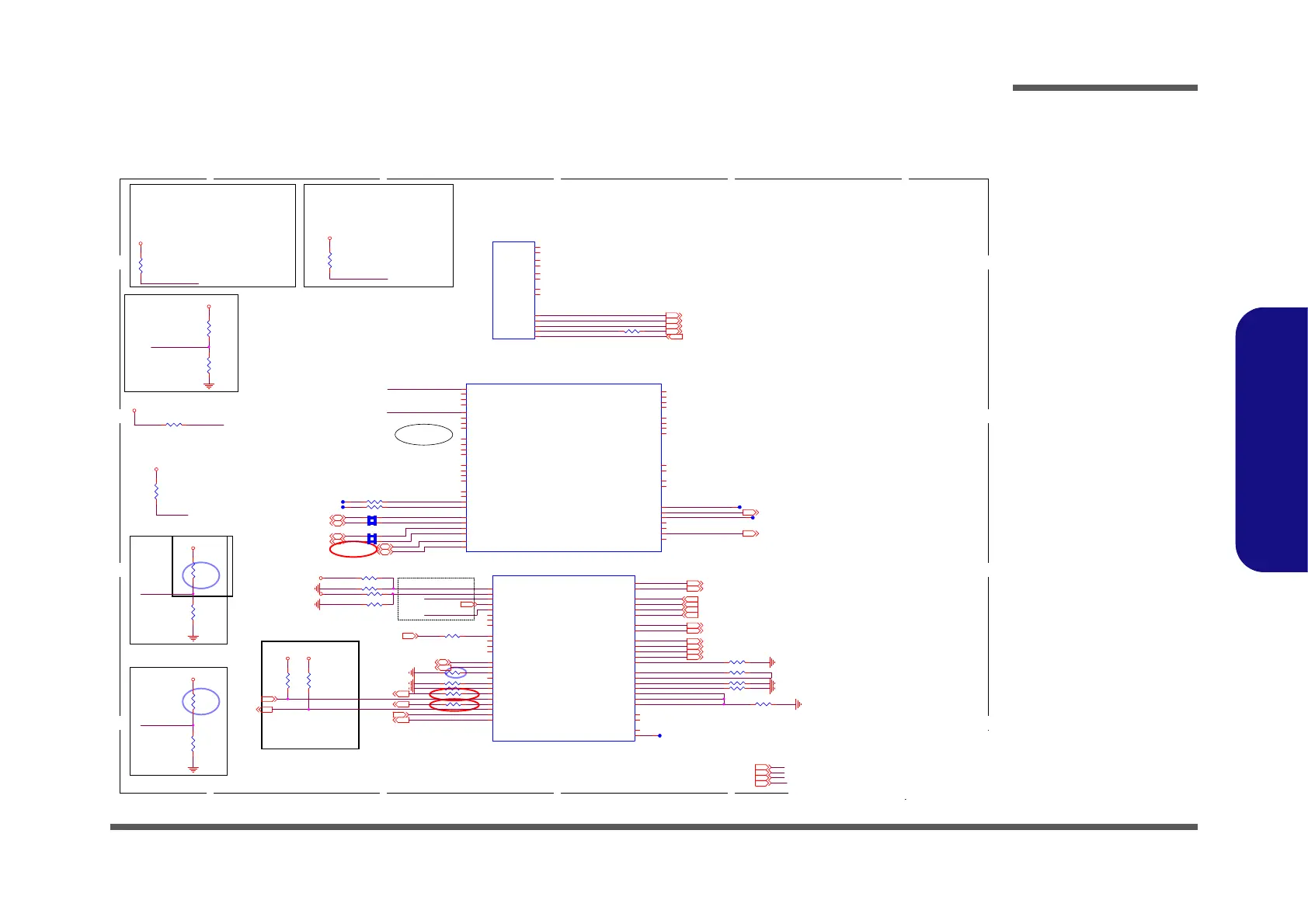

Title

Size Document Number Rev

Date: Sheet

of

6-71-NH5D0-D02

D02

[38] PCH 10_11/12-UART/I2C/GPIO

A3

38 74Friday, February 07, 2020

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Title

Size Document Number Rev

Date: Sheet

of

6-71-NH5D0-D02

D02

[38] PCH 10_11/12-UART/I2C/GPIO

A3

38 74Friday, February 07, 2020

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

R625200_1%_04

R261

100K_04

W/O TPM

R279 *0_06

R278

*4.7K_04

10 OF 13

?

?

?

?

U43J

CML_PCH_H_IP_EXT/BGA

TRIGGER_OUT

AK3

TRIGGER_IN

AK2

CPU_TRST#

AM4

PREQ#

AL2

RSVD4

R32

RSVD3

N32

PRDY#

AM5

RSVD2

AH15

RSVD1

AH14

RSVD8

Y15

RSVD7

Y14

RSVD6

U37

RSVD5

U35

T71

R628150_1%_04

R223200_1%_04

T63

R208

*10K_04

R630100K_04

R207

4.7K_04

11 OF 13

?

?

?

?

U43K

CML_PCH_H_IP_EXT/BGA

GPP_C22/UART2_RTS#

AW21

GPP_C20/UART2_RXD

BD20

GPP_D13/ISH_UART0_RXD/I2C2_SDA

BE17

GPP_C23/UART2_CTS#

AV21

GPP_D12/ISH_SPI_MOSI/GP_BSSB_DI/GSPI2_MOSI

AN18

GPP_C18/I2C1_SDA

BF21

GPP_C19/I2C1_SCL

BE21

GPP_C13/UART1_TXD/ISH_UART1_TXD

AP21

GPP_D14/ISH_UART0_TXD/I2C2_SCL

BF17

GPP_H20/ISH_I2C0_SCL

AG45

GPP_A17/SD_VDD1_PWR_EN#/ISH_GP7

BD38

GPP_C12/UART1_RXD/ISH_UART1_RXD

AU24

GPP_B16/GSPI0_CLK

BF29

GPP_D16/ISH_UART0_CTS#/CNV_WCEN

BF14

GPP_B15/GSPI0_CS0#

BB26

GPP_A23/ISH_GP5

AV34

GPP_D10/ISH_SPI_CLK/GSPI2_CLK

BB20

GPP_H22/ISH_I2C1_SCL

AH47

GPP_A22/ISH_GP4

AW32

GPP_D15/ISH_UART0_RTS#/GSPI2_CS1#/CNV_WFEN

AR18

GPP_H19/ISH_I2C0_SDA

AH46

GPP_C17/I2C0_SCL

BC22

GPP_C16/I2C0_SDA

BF23

GPP_D23/ISH_I2C2_SCL/I2C3_SCL

BE14

GPP_A19/ISH_GP1

BD34

GPP_D11/ISH_SPI_MISO/GP_BSSB_CLK/GSPI2_MISO

BB16

GPP_A21/ISH_GP3

BA33

GPP_D9/ISH_SPI_CS#/GSPI2_CS0#

BA20

GPP_H21/ISH_I2C1_SDA

AH48

GPP_C21/UART2_TXD

BE20

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

BD21

GPP_A18/ISH_GP0

BF35

GPP_A20/ISH_GP2

BE34

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

AW24

GPP_C11/UART0A_CTS#

AP24

GPP_C8/UART0A_RXD

BE23

GPP_D4/ISH_I2C2_SDA/I2C3_SDA/SBK4/BK4

BE15

GPP_C10/UART0A_RTS#

BA24

GPP_C9/UART0A_TXD

BB24

GPP_B21/GSPI1_MISO

BD30

GPP_B22/GSPI1_MOSI

BA26

GPP_B17/GSPI0_MISO

BD29

GPP_B19/GSPI1_CS0#

AW26

GPP_B18/GSPI0_MOSI

BE30

GPP_B20/GSPI1_CLK

AU26

R212

*100K_04

R649*10K_04

R616

20K_04

R25810K_04NH77

R635 30.1_1%_04

R657*10K_04

R629

10K_04

R626200_1%_04

R237100K_04

R268

*0402_short

R211

100K_04

R61522_04

R631

20K_04

R66210K_04

R276

*0402_short

R260

10K_04

TPM

R24875K_1%_04

T64

13 OF 13

?

?

?

?

U43M

CML_PCH_H_IP_EXT/BGA

CNV_WR_CLKN

BD4

CNV_WR_CLKP

BE3

CNV_WR_D0N

BB3

CNV_WR_D0P

BB4

CNV_WR_D1N

BA3

CNV_WR_D1P

BA2

CNV_WT_CLKN

BC5

CNV_WT_CLKP

BB6

CNV_WT_D0N

BE6

CNV_WT_D0P

BD7

CNV_WT_D1N

BG6

CNV_WT_D1P

BF6

CNV_WT_RCOMP

BA1

GPPJ_RCOMP_1P81

BD1

GPPJ_RCOMP_1P82

BE1

GPP_J0/CNV_PA_BLANKING

AV6

GPP_I11/M2_SKT2_CFG0

AP3

GPP_G7/SD_WP

AV13

GPP_G5/SD_CD#

BE8

GPP_I12/M2_SKT2_CFG1

AP2

PCIE_RCOMPN

B12

GPP_J9/CNV_MFUART2_TXD

AU9

GPP_I13/M2_SKT2_CFG2

AN4

GPP_I14/M2_SKT2_CFG3

AM7

PCIE_RCOMPP

A13

GPP_G6/SD_CLK

BD8

GPP_J8/CNV_MFUART2_RXD

AW2

GPP_J10

AV7

TP

AL35

RSVD2

Y35

GPP_J11/A4WP_PRESENT

AR13

RSVD1

BC1

GPP_J2

AW3

GPP_G4/SD_DATA3

BG8

GPP_J3

AT10

GPP_J7/CNV_RGI_RSP/UART0B_CTS#

AV3

GPP_J1/CPU_C10_GATE#

AY3

GPP_J4/CNV_BRI_DT/UART0B_RTS#

AV4

SD_1P8_RCOMP

BE5

GPP_J5/CNV_BRI_RSP/UART0B_RXD

AY2

GPP_J6/CNV_RGI_DT/UART0B_TXD

BA4

SD_3P3_RCOMP

BE4

GPP_G3/SD_DATA2

BF9

GPPJ_RCOMP_1P83

BE2

GPP_G2/SD_DATA1

BF8

RSVD3

Y36

GPP_G0/SD_CMD

AW13

GPP_G1/SD_DATA0

BE9

R283

*0402_short

R62722_04

R22810K_04

R265 *0402_short

R259*10K_04

R665100_1%_04

R270 *0_06

R689

*4.7K_04

LPSS_GSPI0_MOSI

LPSS_GSPI1_MOSI

PCH_2_CPU_TRIGGER_R

BOARD_ID2

DGPU_PWM_SELECT#

3G_CONFIG2

LPSS_GSPI1_MOSI

LPSS_GSPI0_MOSI

SB_BLON

UART2_TXD

UART2_RXD

TPM_DET

TPM_DET

PCIECOMP_N

PCIECOMP_P

BOARD_ID1

CNV_WT_RCOMP

SD3_RCOMP_1P8

SD3_RCOMP_3P3

GPPJ_RCOMP_1P8

CNVI_BRI_DT

CNVI_RGI_DT

GPP_J1

SMI#_R

SMI#_R

SMD_7411_I2C

SMC_7411_I2C

Loading...

Loading...