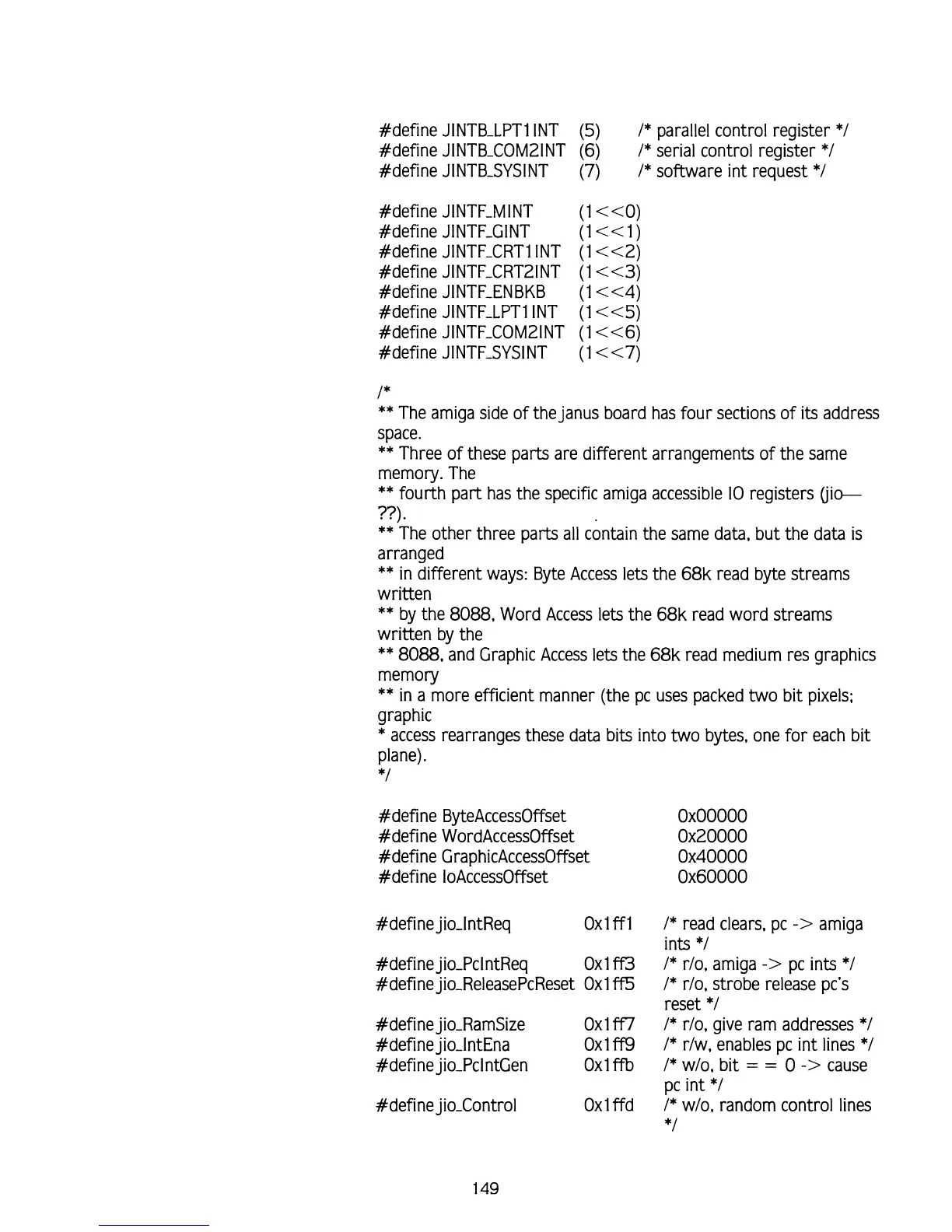

#define JINTB-LPT1 INT

(5)

l*

parallel control register

*/

#define JINTB-COMZINT

(6)

l*

serial control register

*/

#define JINTB-SYSINT

(7)

l*

software int request

*/

#define JINTF-MINT

#define JINTF-GINT

#define JINTF-CRT1 INT

#define

JINTF-CRTZINT

#define JINTF-ENBKB

#define JINTF-LPT1 INT

#define

JINTF-COMZINT

#define JINTF-SYSINT

l*

**

The amiga side of the janus board has four sections of

its

address

space.

**

Three of these parts are different arrangements of the same

memory. The

**

fourth part has the specific amiga accessible

10

registers (jic-

??1.

he he

other three parts all contain the same data, but the data is

arranged

**

in different ways: Byte Access lets the 68k read byte streams

written

**

by the

8088,

Word Access lets the 68k read word streams

written by the

**

8088,

and Graphic Access lets the 68k read medium res graphics

memory

**

in a more efficient manner (the pc uses packed two bit pixels;

graphic

*

access rearranges these data bits into two bytes, one for each bit

plane).

*/

#define ByteAccessOffset Ox00000

#define

WordAccessOffset 0x20000

#define

GraphicAccessOffset 0x40000

#define

loAccessOffset 0x60000

#define

jio-IntReq Oxlffl

l*

read clears, pc

->

amiga

ints

*/

#define jio-PclntReq Oxlff3

l*

r/o, amiga

->

pc ints

*/

#define jio-ReleasePcReset Oxlff5

l*

r/o, strobe release pc's

reset

*/

#define jio-RamSize OxlfV

l*

r/o, give ram addresses

*/

#define jio-IntEna Oxlffg

l*

r/w, enables pc

int

lines

*/

#define jio-PcIntGen Oxlffb /*w/o,bit== 0->cause

pc int

*/

#define jio-Control Oxlffd

l*

w/o, random control lines

*/

Loading...

Loading...