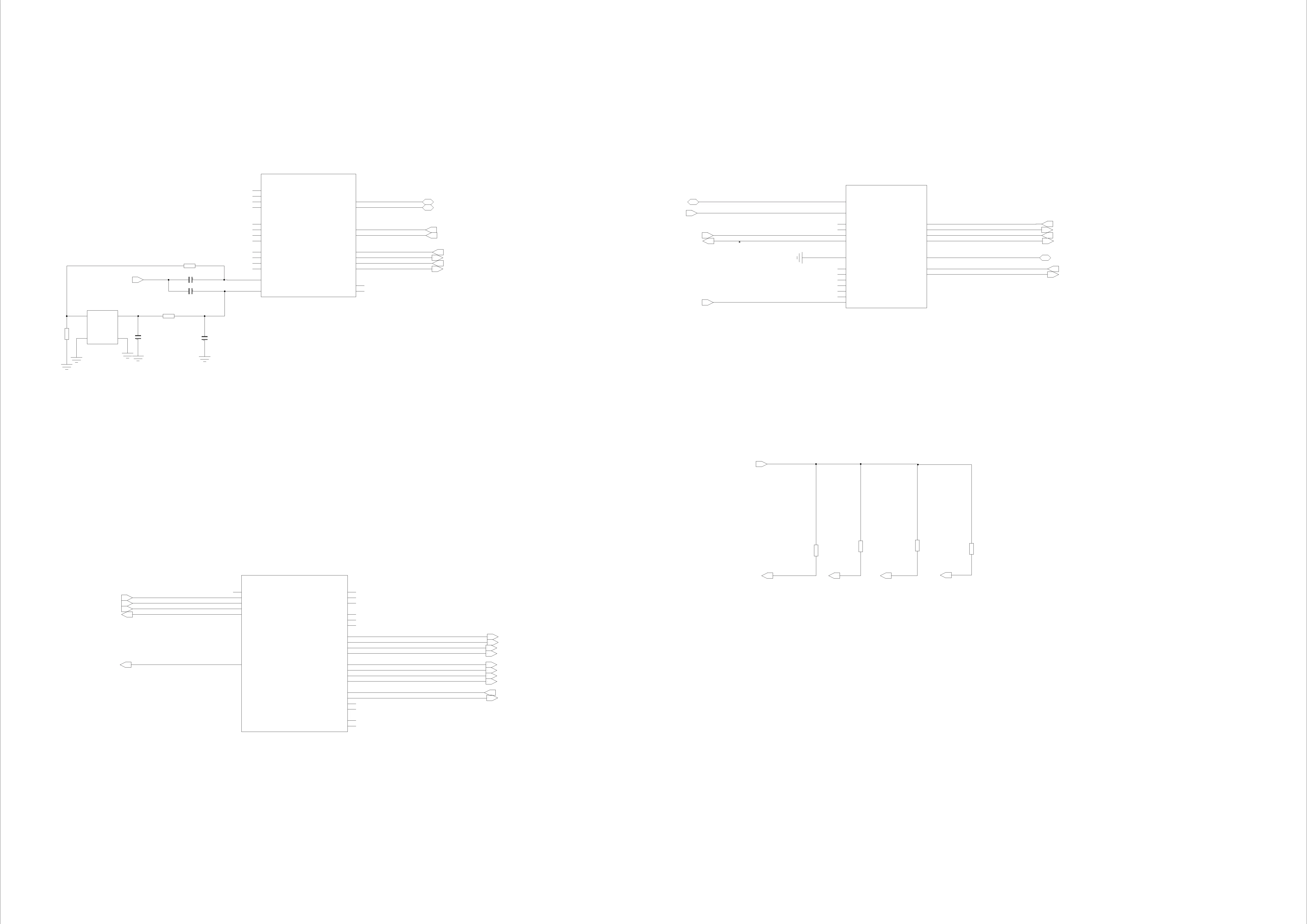

1nF

1

2

NM

C3500

21

R3500

0ohm

C3501

1nF

2

1

WLAN_XO_CLK

1

0ohm

R3501

2

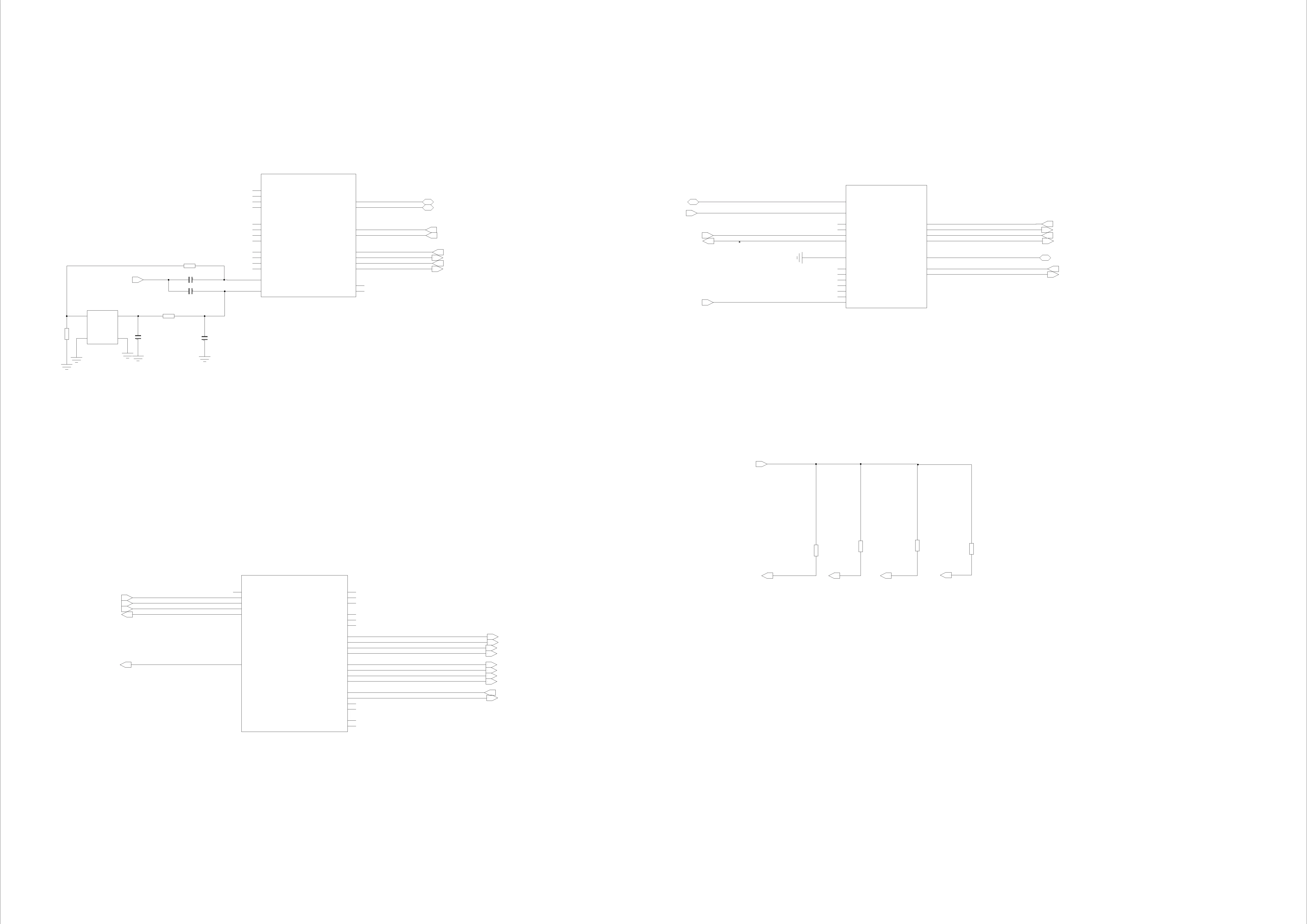

WL_RFRX0_5G

WL_RFPDET0

WL_RFRX1_5G

WL_RFTX0_5G

WL_RFPDET1

BT_I2S_0_SDI

SLEEP_CLK

BTLE_UART_TX

BTLE_UART_RX

MOS_BT_UART_TX

MOS_BT_UART_RX

MOS_BT_UART_RFR

MOS_BT_UART_CTS

CLK_REQ_OUT

C3502

2

6.8pF

1

Reserved

PA_EN_5G_CH0

LNA_EN_5G_CH0

BIAS_SEL_5G_CH0

PA_EN_5G_CH1

LNA_EN_5G_CH1

BIAS_SEL_5G_CH1

VREG_L19B_1P8

R3504

2 1

10Kohm

1

10Kohm

R3502

2

10Kohm

1

R3503

2

SB_DATA{BT_I2S_0_SDI_GPIO)

SB_CLK(BT_I2S_0_SCK_GPIO)

MODE_0

MODE_1

COEX_RXD_GPIO

COEX_TXD_GPIO

ATBH

SRST_N

TCK

TDI

TDO

TMS

TRST_N

LF_CLK_IN_GPIO

CLK_REQ_OUT

UART_RXD_GPIO

UART_TXD_GPIO

UART_CTS_GPIO

UART_RTS_GPIO

SENS_RXD_GPIO

SENS_TXD_GPIO

WCN6750

CTRL1

U3400

T18

V20

T16

R17

P16

T20

W15

U17

W17

Y18

AC19

W19

AB18

V18

Y8

U19

V16

U7

U5

U15

R19

AMB0001889CX

AGPIO_WL_2G

AGPIO_WL_5G_0

AGPIO_WL_5G_1

AGPIO_BT

NC6

NC5

NC7

NC4

NC2

NC3

NC1

NC8

XTALI

XTALO

WLBT_RFTRX0_2G

WLBT_RFTRX1_2G

WL_RFPDET0

WL_RFPDET1

WL_RFRX0_5G

WL_RFTX0_5G

WL_RFRX1_5G

WL_RFTX1_5G

WL_RFPA0_5G

WL_RFPA1_5G

WCN6750

RFA

U3400

A5

B6

E1

B4

D6

B8

B2

D4

A13

A17

K20

H20

N5

M4

L9

K8

M2

N3

M8

M10

L13

M6

K2

M12

AMB0001889CX

WL_GPIO0

WL_GPIO1

WL_GPIO2

WL_GPIO3

WL_GPIO4

SW_CTRL_GPIO

WL_XFEM_CTRL_2G_CH0_0_GPIO

WL_XFEM_CTRL_2G_CH0_1_GPIO

WL_XFEM_CTRL_2G_CH0_2_GPIO

WL_XFEM_CTRL_2G_CH1_0_GPIO

WL_XFEM_CTRL_2G_CH1_1_GPIO

WL_XFEM_CTRL_2G_CH1_2_GPIO

WL_XFEM_CTRL_5G_CH0_0_GPIO

WL_XFEM_CTRL_5G_CH0_1_GPIO

WL_XFEM_CTRL_5G_CH0_2_GPIO

WL_XFEM_CTRL_5G_CH0_3_GPIO

WL_XFEM_CTRL_5G_CH1_0_GPIO

WL_XFEM_CTRL_5G_CH1_1_GPIO

WL_XFEM_CTRL_5G_CH1_2_GPIO

WL_XFEM_CTRL_5G_CH1_3_GPIO

WL_XFEM_CTRL_LAA_RX

WL_XFEM_CTRL_PA_MUTE

WL_XFEM_CTRL_LAA_TXEN_GPIO

WL_XFEM_CTRL_WL_TXEN_GPIO

WL_XFEM_CTRL_WL_TXEN_TO_N79

WL_XFEM_CTRL_N79_TXEN

WCN6750

CTRL2

U3400

P18

P20

U1

P6

P4

N1

N7

R1

R3

R5

P2

T2

T6

T4

N19

M16

N15

Y20

M20

M18

AB12

AA11

AC11

AA9

W9

Y10

AMB0001889CX

6.8pF

C3503

1

2

WL_RFTX1_5G

CLOCK CONFIGURATION 1) PMIC CLK TO WCN6750 XTALO R3504=R3502=R3503=NM 2)76.8MHZ XTAL TO WCN6750(CLK_CFG=1, CLK_SEL[0]=1, XO_TCXO_SEL=1) R3504=R3502=R3503=10K

5G_RFFE_SEL4_CH0

5G_RFFE_SEL4_CH1

WLBT_RFTRX0_2G

WLBT_RFTRX1_2G

WLAM_COEX_UART_TX

WLAM_COEX_UART_RX

BT_I2S_0_SCK

WL_UART_TX

SW_CTRL

WL_UART_TX

WLAN2HOST_SOL

WLAN2HOST_SOL WL_GPIO 2

10Kohm

2 1

R3505

CLK_REQ_OUT

CLK_REQ_OUT

NM

HOST2WLAN_SOL

WL_GPIO 2

BOOTSTARPS

PA_MUTE

LAA RX

XTAL1 XTAL2

GND1 GND2

7AH07680A04

Q3500

42

31

C3504

12

0ohm

NM

NM

NM

NM

NM

NM

Loading...

Loading...