VM88 VM88

4 41

1. SPECIFICATIONS

Specification Unit 0 dBV = 1 Vr.m.s., 0 dBu = 0.775 Vr.m.s.

Standard Input

INPUT 1 ~ 4

Connector XLR Cannon (MIC)

Ø 6 mm TRS phone jack (LINE)

Input level -50 dBu ~ -10 dBu (MIC)

-30 dBu ~ +10 dBu (LINE)

Input impedance 3 kΩ or more (MIC)

10 kΩ or more (LINE)

INPUT 5 - 8

Connector Ø 6 mm TRS phone jack

Input level -40 dBu ~ +4 dBu

Input impedance 10 kΩ or more

INSERT 1 - 4

Connector Ø 6 mm TRS phone jack

Input level -10 dBV

Input impedance 10 kΩ or more

MON IN L, R

Connector Ø 6 mm TRS phone jack

Input level -10 dBV

Input impedance 10 kΩ or more

DATA IN

Connector Square shape optical

Format

S/P DIF IN IEC consumer optical standard (IEC 958 Part 3)

ADAT IN Alesis Proprietary Multichannel Optical Digital Interface

Standard Output

STEREO OUT L, R

Connector XLR Cannon

Ø 6 mm TRS phone jack

Output level +4 dBu (XLR Cannon)

-10 dBV (Ø 6 mm TRS phone jack)

Load impedance 10 kΩ or more (XLR Cannon & Ø 6 mm TRS phone jack)

AUX SEND 1, 2

Connector Ø 6 mm TRS phone jack

Output level -10 dBV

Load impedance 10 kΩ or more

MON OUT L, R

Connector Ø 6 mm TRS phone jack

Output level -10 dBV

Load impedance 10 kΩ or more

PHONES OUT L, R

Connector Ø 6 mm TRS phone jack

Output level 50 mW or more

Load impedance 32 Ω

DATA OUT

Connector Square shape optical

Format

S/P DIF OUT IEC consumer optical standard (IEC 958 Part 3)

ADAT OUT Alesis Proprietary Multichannel Optical Digital Interface

EQ

HI 10 kHz ± 18 dB (shelving type)

MID 1 kHz ± 18 dB (peaking type)

LO 100 Hz ± 18 dB (shelving type)

Fader (VR) Position at Standard Input / Output

Input Fader 80 position

INPUT 1 ~ 4 (TRS) +10 dBu, 1 kHz

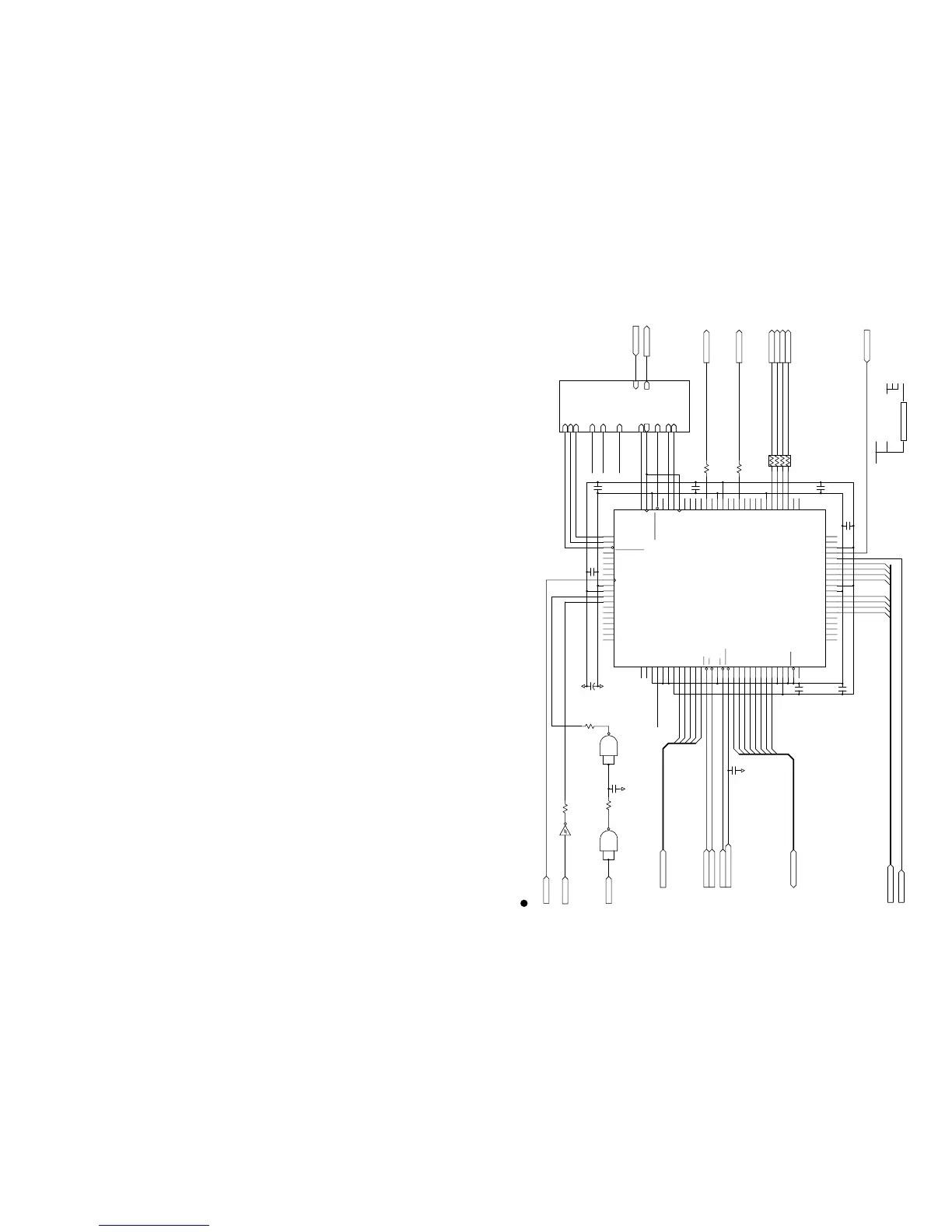

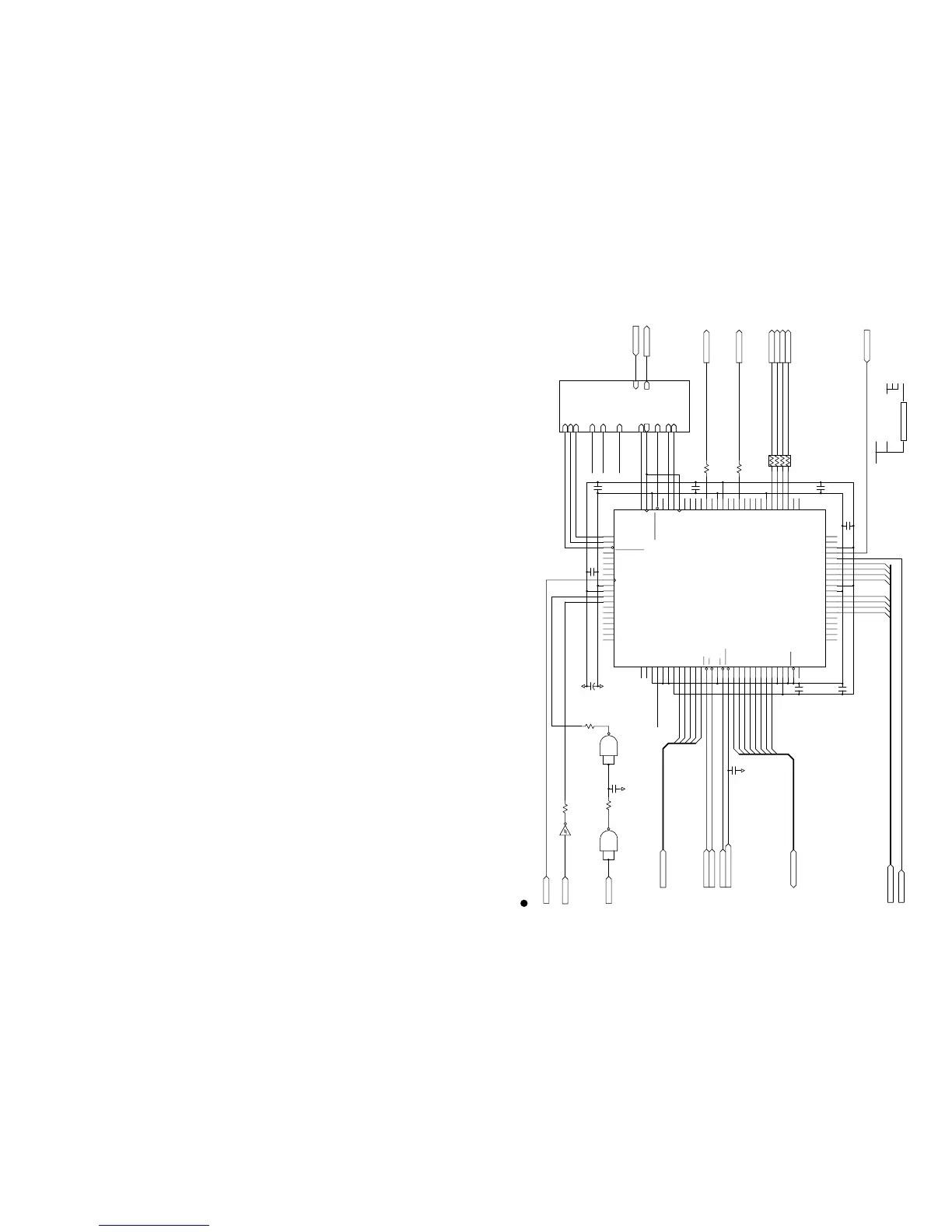

DIGITAL I/F, DIGITAL, MAIN, VM88

C6

0.0 1

C7

0.0 1

C8

0.0 1

DGND

D+5

C30

100P

C9

0.0 1

C10

0.0 1

C26

10/16

//

R9 6 4

100

R965

100

2

4

6

87

5

3

1

R967

DGND

C11

0.0 1

C12

0.0 1

U918

GA_DIF

R966

100

5 6

U903C

12

13

11

U913D

9

10

8

U914C

R40

47

C44

100P

DGND

R41

100

TDO_FS0O

TDO_EMPO

PI

PO

TEST1

TEST2

VDD

A4

A3

A2

A1

A0

WR

RD

VSS

CS

RESET

D0

D1

D2

D3

D4

D5

D6

D7

CTL_PIN

VDD

VSS

EN_IF

SINA_MD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

PD2

MCK2

VSS

PLL1_CONT

LOCK1

FCONT1

PD1

MCK1

DO_SEL0

DO_SEL1

ADAT_MD

DO2

DO1

DO_EMPI

VSS

VDD

DO_FS0I

DO_FS1I

SOUT_DI

SOUT2_78

SOUT2_56

SOUT2_34

SOUT2_12

VSS

SOUT1_78

SOUT1_56

SOUT1_34

SOUT1_12

DI_EMPO

DI_FS0O

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

TDO_FS1O

W_OUT

W_IN2

W_IN1

FS256O

BCKO

LRCKO

LRCKI

BCKI

VDD

VSS

FS256I

PCMBW0

PCMBW1

CK_SEL0

CK_SEL1

CK_SEL2

PLL2_CONT

LOCK2

FCONT2

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

SOUT1_MD

SOUT2_MD

TDI_FS1I

TDI_FS0I

TDI_EMPI

SINA_12

SINA_34

SINA_56

SINA_78

VSS

VDD

SINB_12

SINB_34

SINB_56

SINB_78

SIN_DIF

DI1

DI2

DI_SEL

DI_FS1O

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

ADO1

ADO2

ADO3

ADO4

ADOA

ADO2

ADO3

ADO4

A4

A3

A2

A1

A0

D0

D1

D2

D3

D4

D5

D6

D7

SPDIF//ADAT

/PLL2_CONT

LOCK2

FCONT2

PLL

LRCK

LRCK

DATA_IN

SPDIF//ADAT

DATA_IN

SPDIF//ADAT

/PLL2_CONT

LOCK2

FCONT2

pll.sch

PD1

FCONT1

MCK

/PLL1_CONT

PD2

PD1

FCONT1

MCK

/PLL1_CONT

PD2

EXT//INT

FS512

EXT//INT

FS512

EXT//INT

FS512

DATA_OUT

SPDIFOUT

DATA_OUT

SPDIFOUT

SOUT_78

SOUT_56

SOUT_34

SOUT_12

SOUT_78

SOUT_56

SOUT_34

SOUT_12

100 X 4

DATA_IN

DATA_IN

STOUT

ADO[1...4]

STOUT

ADO[1...4]

/RST_DIF

/CS_DIF

/RD_DIF

/WR_DIF

CPU> D[0...7]

CPU>

CPU>

CPU>

CPU>

/RST_DIF

/CS_DIF

/RD_DIF

/WR_DIF

D[0...7]

A[0...4]

CPU>

A[0...4]

/LRCK

/LRCK

BCK

BCK

FS256

FS256

LRCK

74VHC00

74VHC00

74VHC14

2. MAIN_D, CPU

1. MAIN_D, ROOT

3. MAIN_D, DSP_ROOT

7. MAIN_D, GA_DIF

4. MAIN_D, DSP1 2

5. MAIN_D, DSP3

6. MAIN_D, DSP SEL

8. MAIN_D, PLL

Loading...

Loading...