--------------------------------------------------------HMCS45C,HMCS45CL

Table 2 Example of Pattern Instruction Usage

Before Execution

Referred

After Execution

ROM

Pattern

PC

Value

P

C B

A

Address

B A

R2

R3

0-3F

1

0 A 0

10-20

120

2 B

- -

0-3F 7 1 4 0

61-00

220

-

-

4

B

30-00

4

0/1

0 9

62-09

320

2 B 4

B

30-00

4

0/1

F 9

63-39

"-"

means

that

the

value is

unchanged

after

the

execution.

"0/'"

means

that

either "0" or

"'"

will

do.

• BRANCH

ROM

is

accessed according to the program counter sequence

and the program

is

executed. In order

to

jump to any address out

of

the sequence, there are four

ways.

o They are explained

in

the following paragraphs.

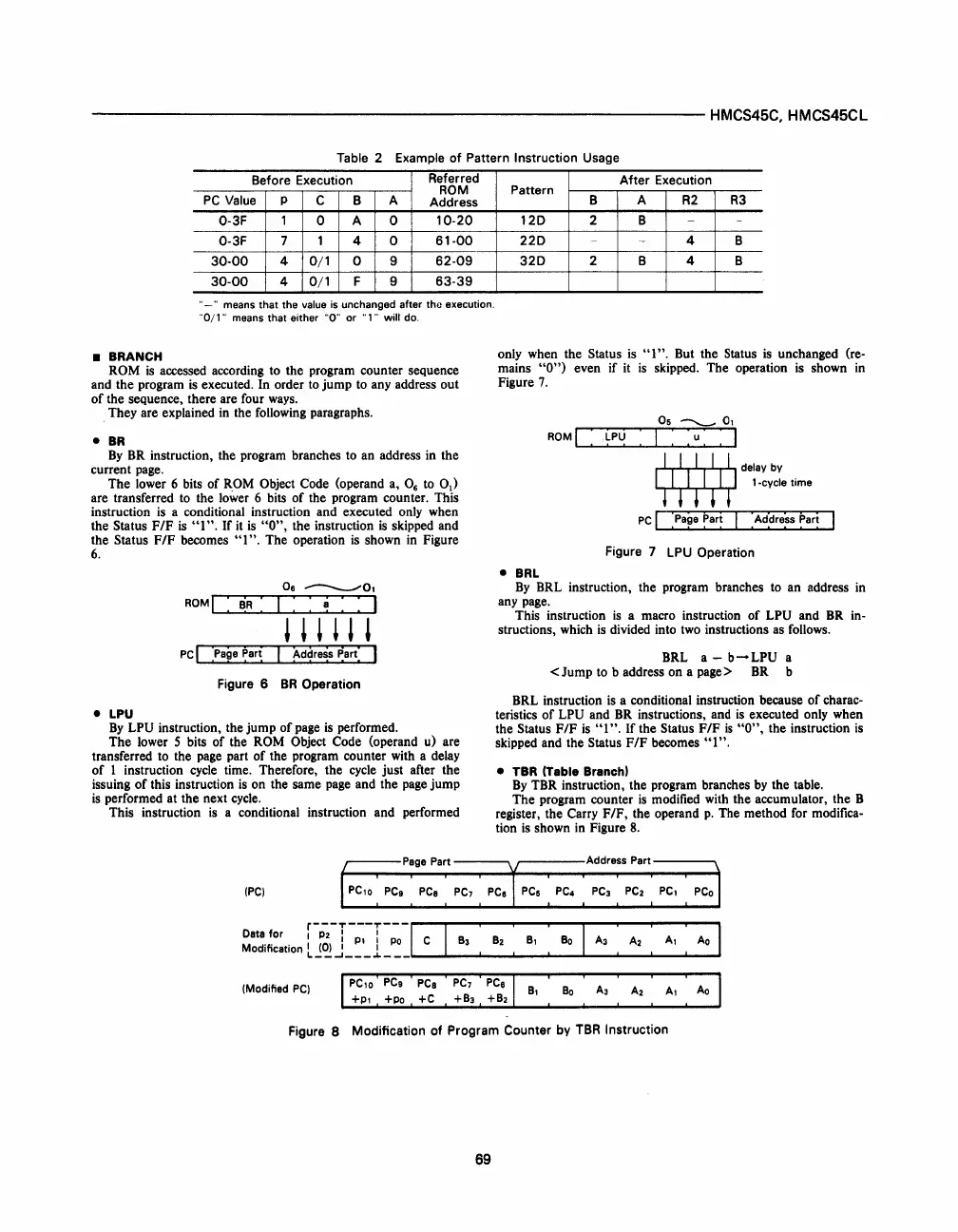

•

BR

By

BR

instruction, the program branches to an address

in

the

current

page.

The lower 6 bits of

ROM

Object Code (operand a, 0

6

to

0

1

)

are transferred

to

the lower 6 bits

of

the program counter. This

instruction

is

a conditional instruction and executed only when

the Status F

IF

is

"1".

If

it

is

"0",

the instruction

is

skipped and

the Status F

IF

becomes

"1".

The operation

is

shown

in

Figure

6.

06

__

0,

ROMI

~R:

I : :

~

: : I

"""

Figure 6

BR

Operation

•

LPU

By

LPU instruction, the jump of page

is

performed.

The lower 5 bits of the

ROM

Object Code (operand u) are

transferred to the

page

part

of

the program counter with a delay

of

1 instruction

cycle

time. Therefore, the

cycle

just after the

issuing

of

this instruction

is

on the same

page

and the

page

jump

is

performed at the next

cycle.

This instruction

is

a conditional instruction and performed

only when the Status

is

"1".

But the Status

is

unchanged (re-

mains

"0")

even if

it

is

skipped. The operation

is

shown

in

Figure

7.

•

BRL

05

_______

0,

ROM

I

~P~:

I : :

u:

: I

~delaYbY

Yiffl

'-cycle

time

Figure 7

LPU

Operation

By

BRL

instruction, the program branches to an address

in

any

page.

This instruction

is

a macro instruction

of

LPU and

BR

in-

structions, which

is

divided into

two

instructions as follows.

BRL

a -

b-LPU

a

<Jump

to b address on a page>

BR

b

BRL

instruction

is

a conditional instruction because

of

charac-

teristics

of

LPU and

BR

instructions, and

is

executed only when

the Status

FIF

is

"1".

Ifthe

Status

FIF

is

"0",

the instruction

is

skipped and the Status F

IF

becomes

"1".

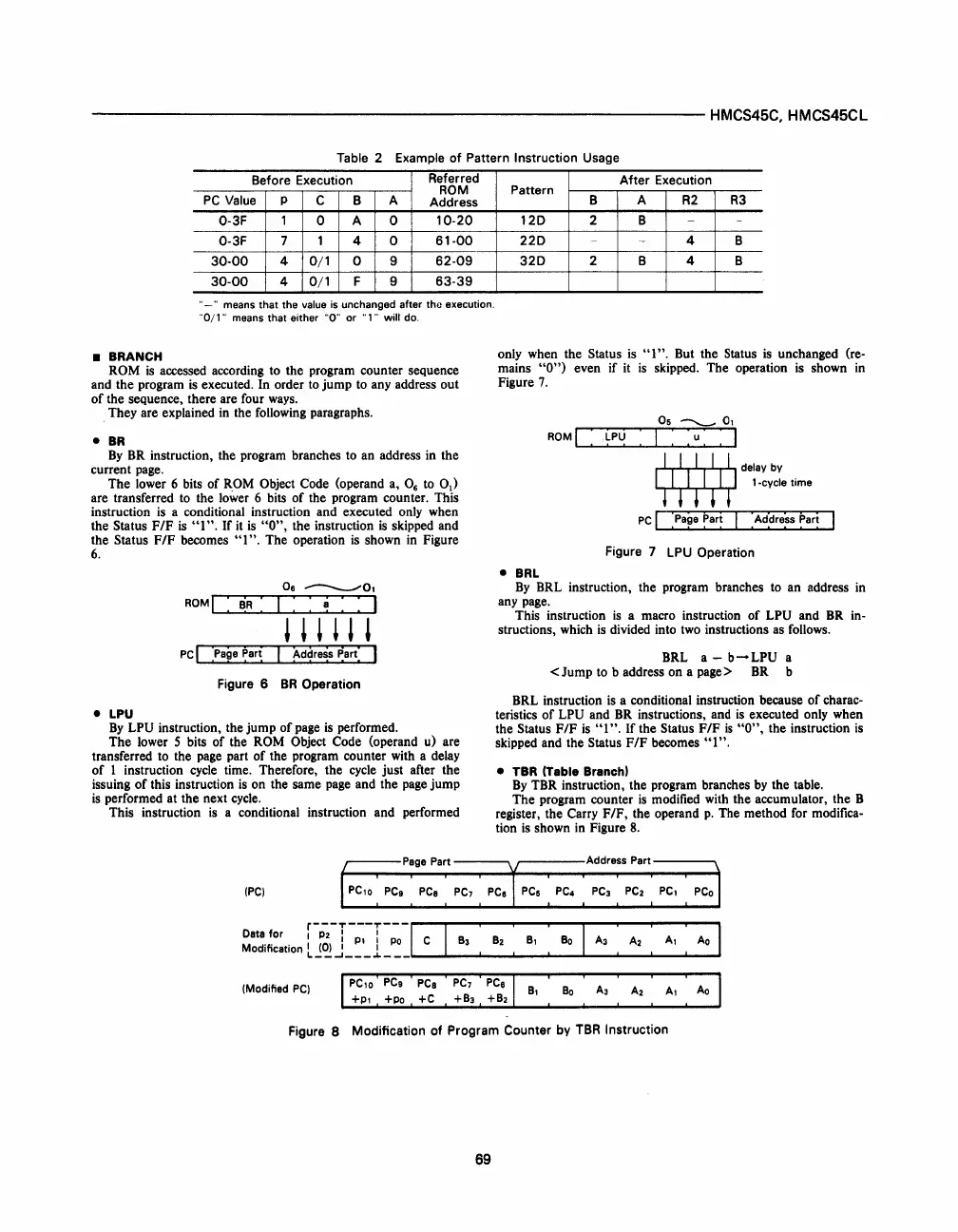

• TBR (Table Branch)

By

TBR

instruction, the program branches

by

the table.

The program counter

is

modified with the accumulator, the B

register, the Carry

FIF,

the operand

p.

The method for modifica-

tion

is

shown

in

Figure

8.

,-------Page

Part

---""

r----Address

Part

----..

(PC)

r---

T

---,---

: :

Data for I

P2

:

PI

:

Modification

LJ~J

____

LP~-'

C

B3

B2

B,

Bo

A3

A2

A,

Ao

(Modified

PC)

PC,o

PCg

PCs

PC7

PCe

B,

Bo

A3

A2

A,

Ao

+p,

+Po

+C

+B3

+B2

Figure 8

Modification of Program Counter

by

TBR

Instruction

69

Loading...

Loading...