hipot.com 54

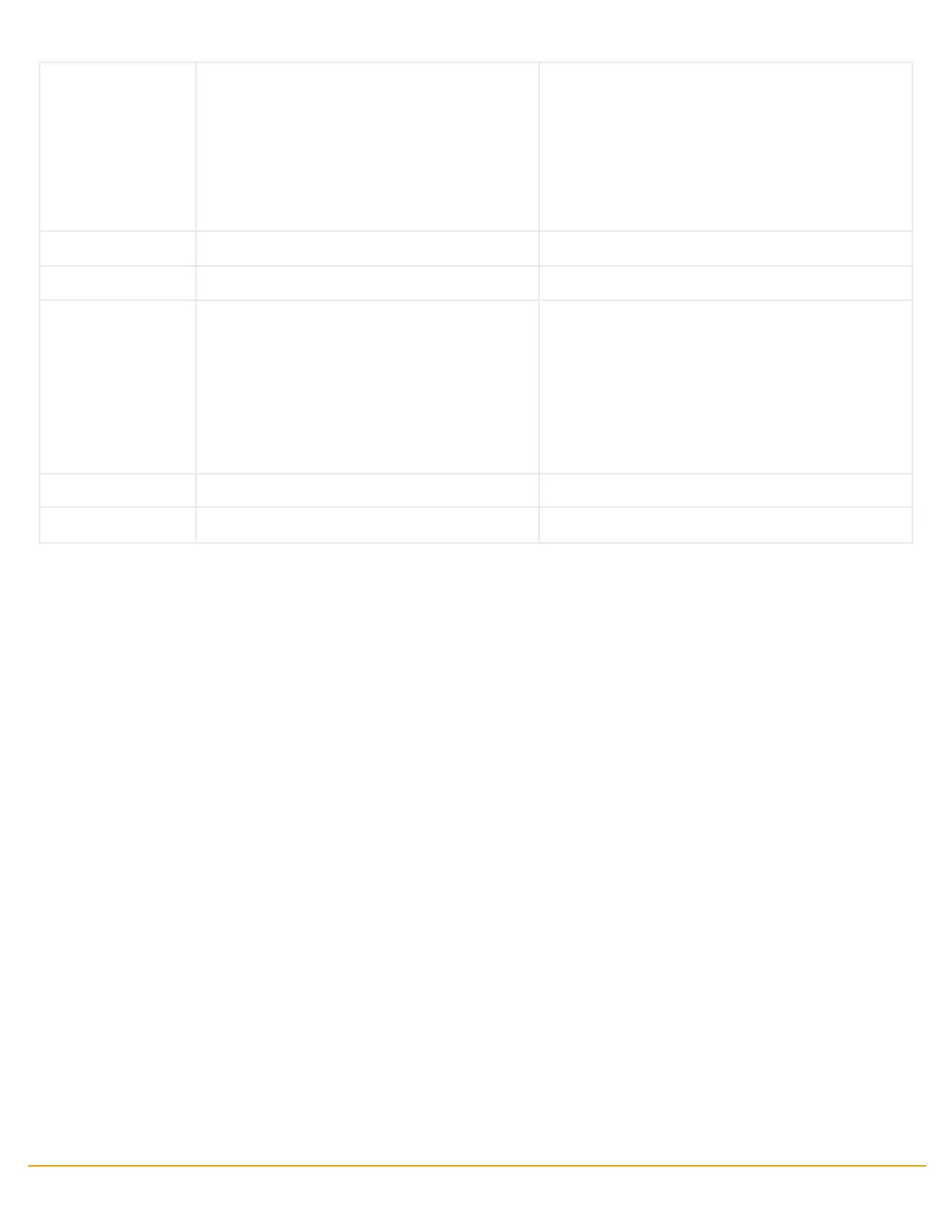

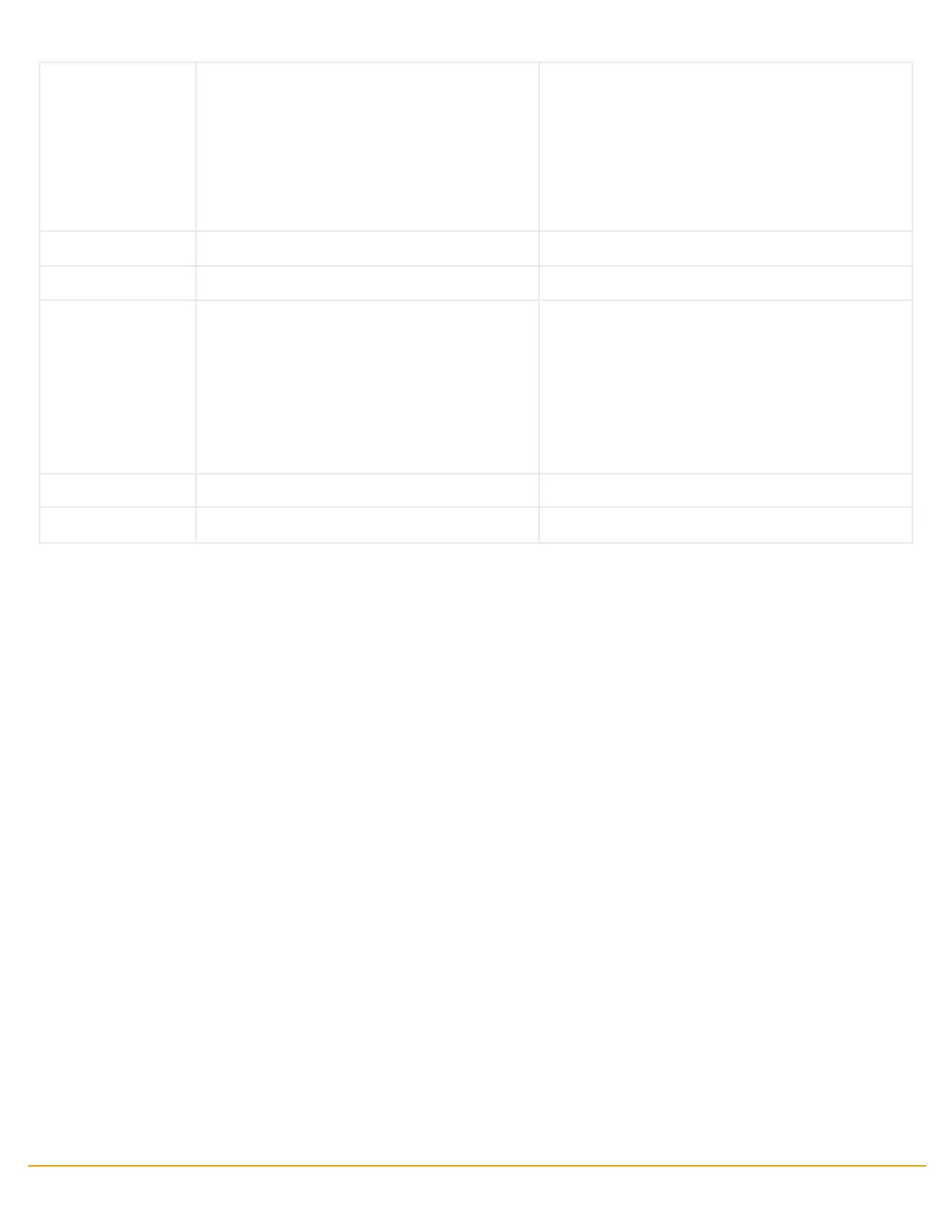

*ESR? Standard Event Status Register Query BIT 0, 01H,(1) Operation Complete

BIT 1,02H,(2) Not Used

BIT 2,04H,(4) Query Error

BIT 3,08H,(8) Device Error

BIT 4,10H,(16) Execution Error

BIT 5,20H,(32) Command Error

BIT 6,40H,(64) Not Used

BIT 7,80H,(128) Power On

*ESE <value> Standard Event Status Enable Command value = 0 - 255

*ESE? Standard Event Status Enable Query 0 - 255

*STB? Read Status Byte Query BIT 0, 01H,(1) ALL PASS

BIT 1,02H,(2) FAIL

BIT 2,04H,(4) ABORT

BIT 3,08H,(8) PROCESS

BIT 4,10H,(16) Message Available

BIT 5,20H,(32) Standard Event (ESB)

BIT 6,40H,(64) Request Service (MSS)

BIT 7,80H,(128) PROMPT

*SRE <value> Service Request Enable Command value = 0 - 255

*SRE? Service Request Enable Query 0 - 255

*IDN? - Read the tester identication string. Company =SLA.

*RST - Reset the tester to original power on conguration. Does not clear Enable register for Standard Summary Status or

Standard Event Registers. Does not clear the output queue. Does not clear the power-on-status-clear ag.

*TST? - Performs a self test of the tester data memory. Returns 0 if it is successful or 1 if the test fails.

*CLS - Clears the Status Byte summary register and event registers. Does not clear the Enable registers.

*OPC - Sets the operation complete bit (bit 0) in the Standard Event register after a command is completed.

*OPC? - Returns an ASCII “1” after the command is executed.

*WAI - After the command is executed, it prevents the tester from executing any further query or commands until the no-

operation-pending ag is TRUE.

*PSC {1|0} - Sets the power-on status clear bit. When set to 1 the Standard Event Enable register and Status Byte Enable

registers will be cleared when power is turned ON. 0 setting indicates the Enable registers will be loaded with Enable register

masks from non-volatile memory at power ON.

*PSC? - Queries the power-on status clear setting. Returns 0 or 1.

*ESR? - Queries the Standard Event register. Returns the decimal value of the binary-weighted sum of bits.

*ESE <value> - Standard Event enable register controls which bits will be logically ordered together to generate the Event

Summary bit 5 (ESB) within the Status Byte.

Loading...

Loading...