Introduction

› The Queued Synchronous Peripheral Interface (QSPI) enables any

synchronous serial communication with external devices based on the

standardized SPI-bus signals: clock, data-in, data-out and slave select.

› The QSPI works in full duplex mode either as Master or Slave with up to

50 Mbit/s.

› The DMA module channels can be configured to transfer data from/to

QSPI FIFOs to/from internal RAM Memory without any CPU intervention.

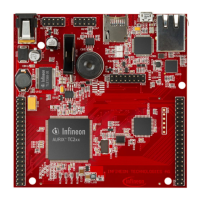

› This example is based on the Infineon Low Level Drivers to demonstrate

SPI Master Slave Communication with minimum CPU intervention.

3

2020-01-17 Copyright © Infineon Technologies AG 2020. All rights reserved.

Loading...

Loading...