MEMORY INTERFACING

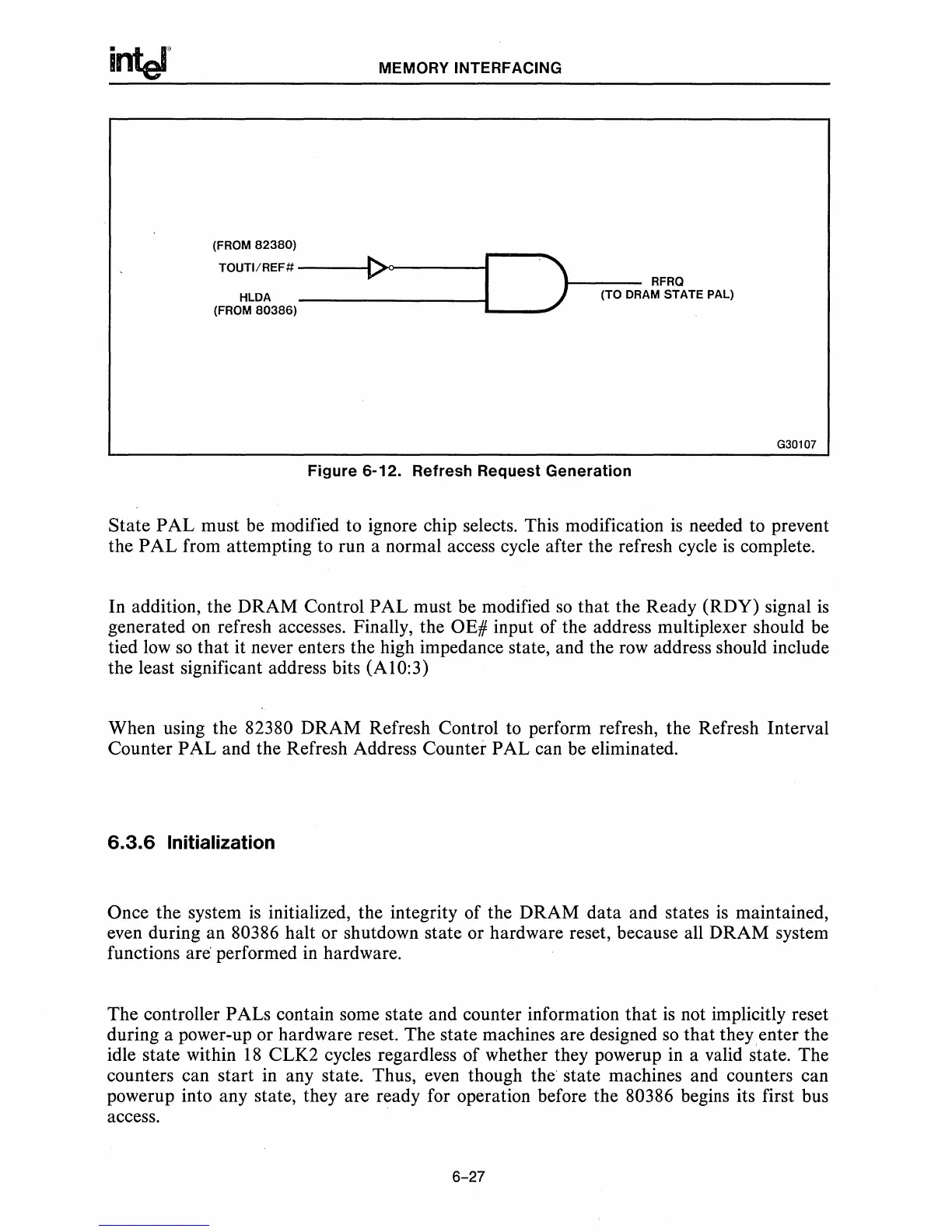

(FROM

82380)

TOUTI/REF#

----il>c-------I

)

HLDA

---------t

__

-'

I---(T-O-D-RA~F:~TE

PAL)

(FROM

80386)

-

G30107

Figure

6-12.

Refresh

Request

Generation

State

PAL

must be modified to ignore chip selects. This modification

is

needed to prevent

the

PAL

from attempting to run a normal access cycle after the refresh cycle

is

complete.

In addition, the DRAM Control

PAL

must be modified

so

that

the Ready (RDY) signal

is

generated on refresh accesses. Finally, the OE# input

oUhe

address multiplexer should

be

tied

low

so

that

it never enters the high impedance state, and the row address should include

the least significant address bits (A1O:3)

When using the 82380

DRAM

Refresh Control to perform refresh, the Refresh Interval

Counter

PAL

and the Refresh Address Counter PAL can be eliminated.

6.3.6

Initialization

Once the system

is

initialized, the integrity of the DRAM data and states

is

maintained,

even during an 80386 halt or shutdown state or hardware reset, because all DRAM system

functions

are

performed in hardware.

The controller PALs contain some state and counter information

that

is

not implicitly reset

during a power-up or hardware reset. The state machines are designed

so

that they enter the

idle state within

18

CLK2 cycles regardless of whether they powerup in a valid state. The

counters can start in any state. Thus, even though the state machines and counters can

powerup into any state, they are ready for operation before the 80386 begins its first bus

access.

6-27

Loading...

Loading...