MEMORY INTERFACING

Some DRAMs require a number of warm-up cycles before they can operate. Either method

listed below can provide these cycles:

• Performing several dummy DRAM cycles

as

part of the 80386 initialization process.

Setting up the 80386 registers and performing a REP LODS instruction

is

one way to

perform these dummy cycles.

• Activating the

RFRQ

signal, using external logic, for a preset amount of time, causing

the DRAM control hardware to run several refresh cycles.

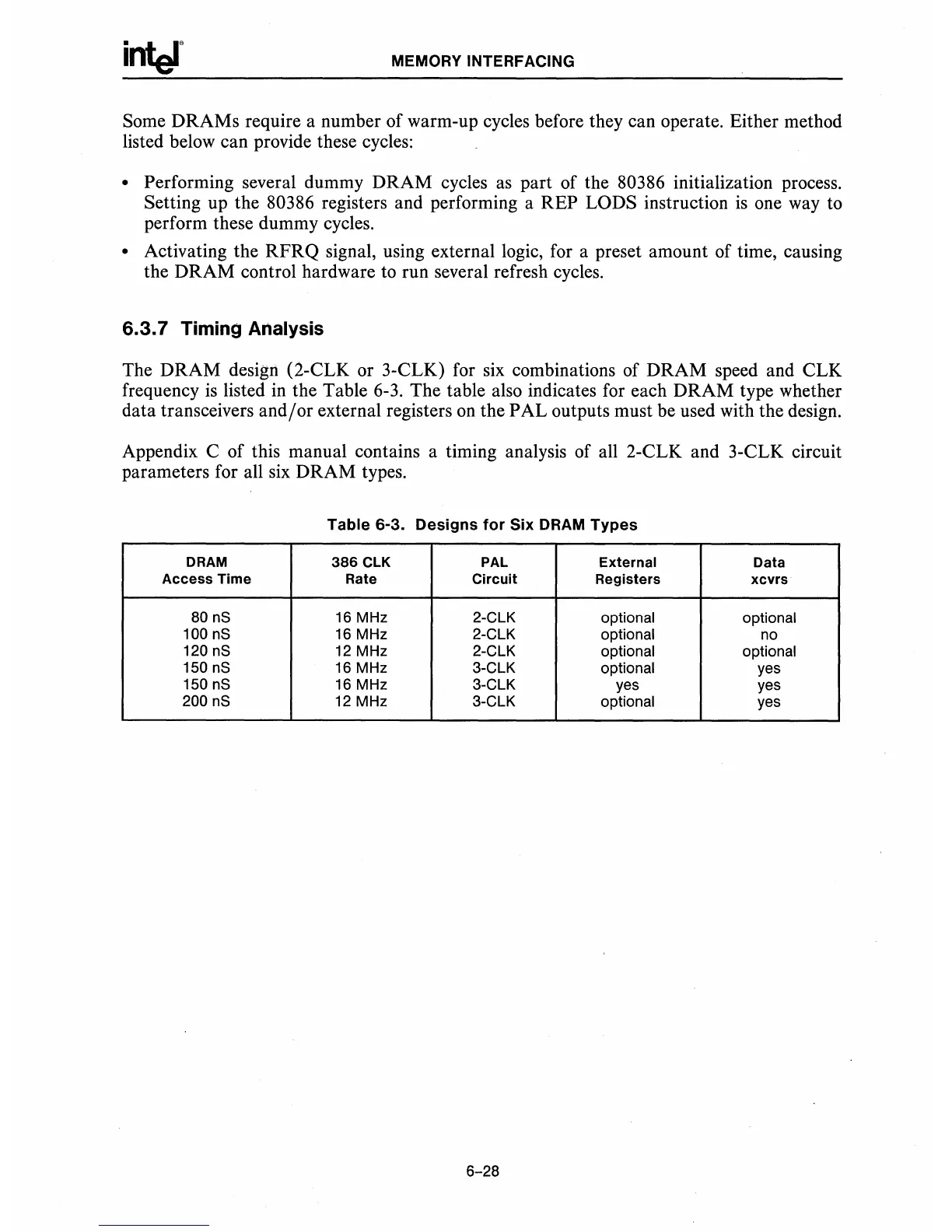

6.3.7 Timing Analysis

The

DRAM

design (2-CLK or 3-CLK) for six combinations of DRAM speed and CLK

frequency

is

listed in the Table 6-3. The table also indicates for each DRAM type whether

data transceivers

and/or

external registers

on

the PAL outputs must be used with the design.

Appendix C of this manual contains a timing analysis of all 2-CLK and 3-CLK circuit

parameters for all six DRAM types.

Table

6-3.

Designs

for

Six

DRAM

Types

DRAM

386

elK

PAL External Data

Access

Time Rate Circuit Registers

xcvrs

80 nS 16 MHz 2-ClK

optional optional

100 nS 16 MHz 2-ClK

optional no

120 nS 12 MHz

2-ClK

optional

optional

150 nS 16 MHz 3-ClK optional

yes

150 nS

16 MHz

3-ClK

yes

yes

200 nS

12 MHz

3-ClK

optional

yes

6-28

Loading...

Loading...