CHAPTER

7

CACHE

SUBSYSTEMS

Operating at

20

MHz, the 80386 can perform a complete bus cycle in only

100

nanoseconds,

for a maximum bandwidth of 40 megabytes per second. To sustain this maximum speed, the

80386 must

be

matched with a high-performance memory system. The system must be fast

enough to complete bus cycles with

no

wait states and large enough to allow the 80386 to

execute large application programs.

Traditional memory systems have been implemented with dynamic RAMs (DRAMs), which

provide a large amount of memory for a small amount of board space and money. However,

no common low-cost DRAMs are available that can complete every bus cycle in

100 nanoseconds. Faster static RAMs (SRAMs) can meet the bus timing requirement, but

they offer a relatively small amount of memory at a higher cost. Large SRAM systems can

be prohibitively expensive.

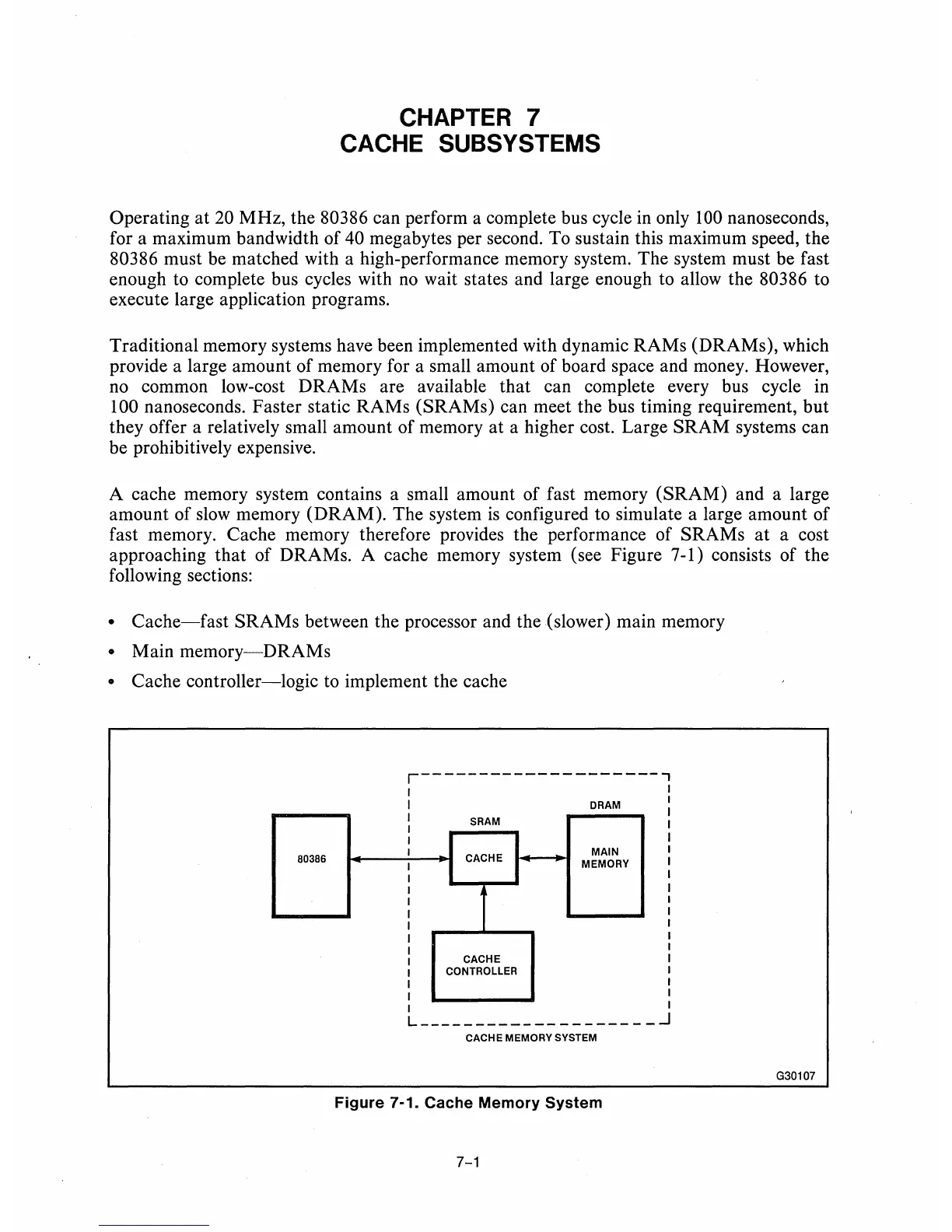

A cache memory system contains a small amount of fast memory (SRAM) and a large

amount of slow memory (DRAM). The system

is

configured to simulate a large amount of

fast memory. Cache memory therefore provides the performance of SRAMs at a cost

approaching that of DRAMs. A cache memory system (see Figure 7-1) consists of the

following sections:

•

Cache-fast

SRAMs between the processor and the (slower) main memory

• Main

memory-DRAMs

• Cache

controller-logic

to implement the cache

r--------------------,

DRAM

SRAM

80386

: CACHE

r--

MAIN

MEMORY

1

CACHE

CONTROLLER

L

____________________

~

CACHE MEMORY SYSTEM

G30107

Figure 7-1. Cache Memory System

7-1

Loading...

Loading...