CACHE SUBSYSTEMS

31

32.BIT

PROCESSOR

ADDRESS

SELECT

130 16

1

15

INDEX

INDEX

TAG

FFFC

01

FFF8 FF

0010

OOOC

0008

00

0004

01

0000

00

(14

BITS) I

~

BYTE:

I

64KsRAM

/-64K

CACHE = 16

BITs-.J

1-2

GIGABYTE

DRAM

-

31

BYTEs~

DATA

INDEX

FFFC

11223344 FFF8

DATA

0010

OOOC

12345678

11223344

L.J

0008

0004

0000

-

-

-

87654321

~

'""-

11235813

12345678

13579246

I-

FFFC

FFF8

j.32BITs.j

0010

OOOC

0008

CACHE

-

11235813 0004

0000

FFFC

FFF8

0010

OOOC

87654321

0008

0004

13579246

DilDO

j.32BlTs.j

TAG

)

,~,

1=,

j-

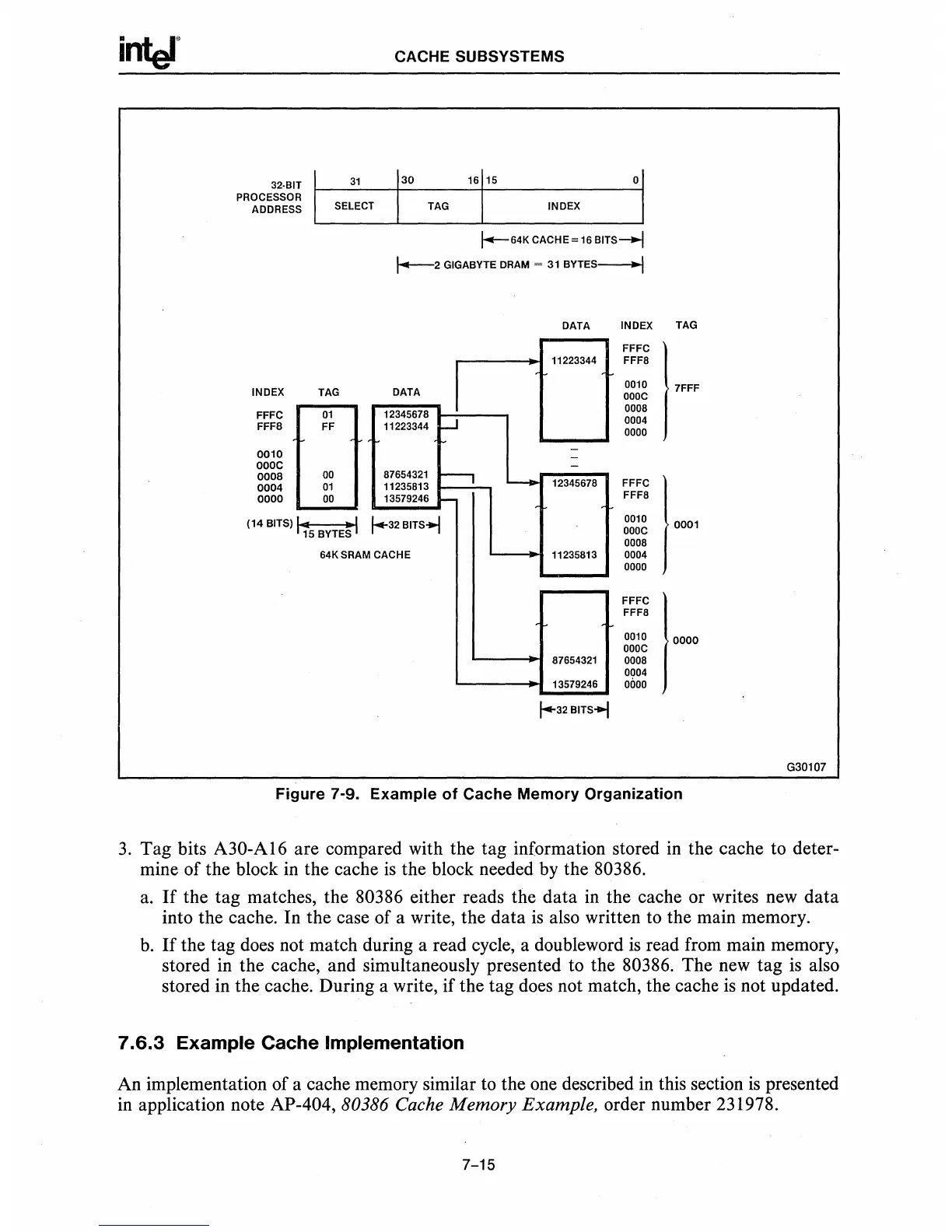

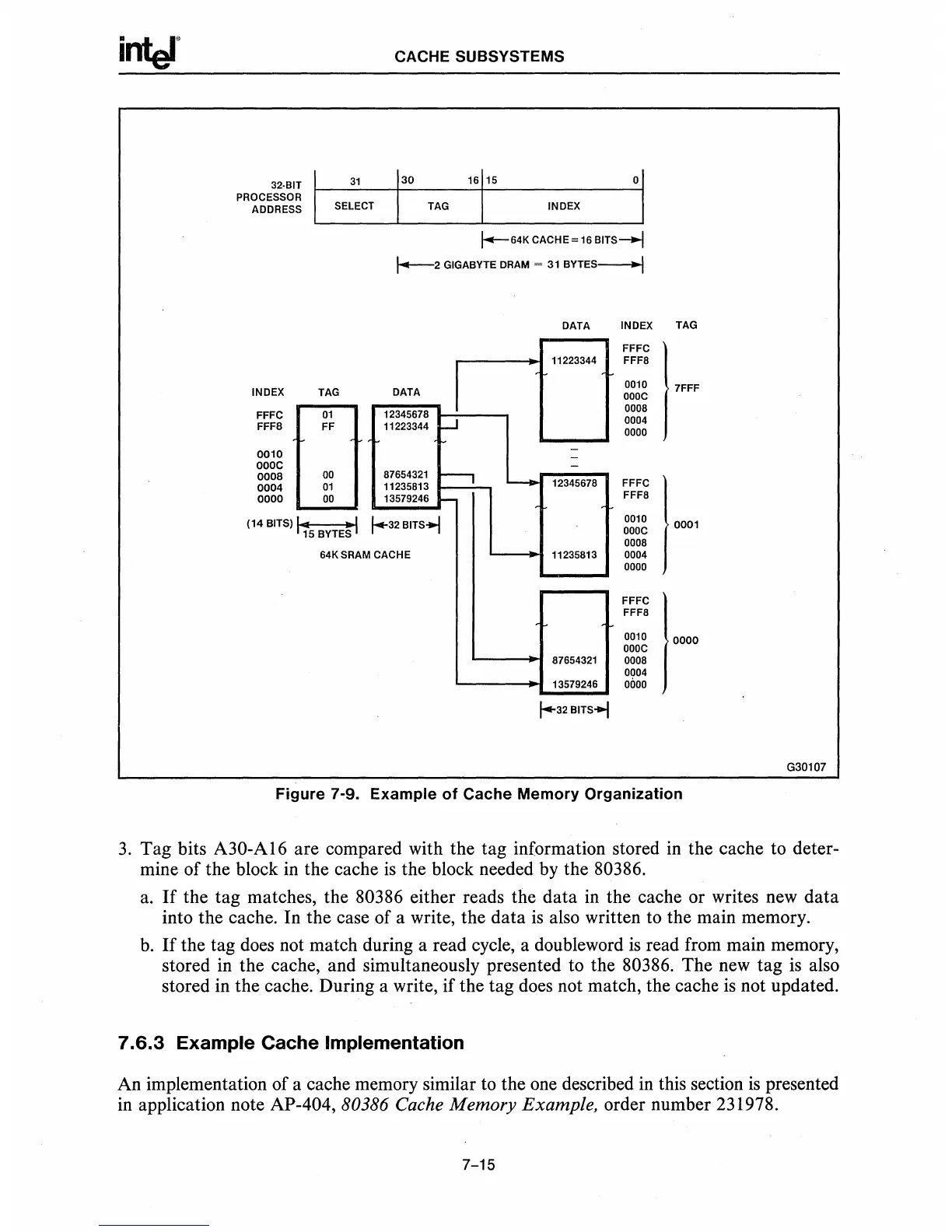

Figure 7-9. Example of Cache Memory Organization

G30107

3.

Tag bits A30-A16 are compared with the tag information stored

in

the cache to deter-

mine of the block in the cache

is

the block needed by the 80386.

a.

If

the tag matches, the 80386 either reads the data

in

the cache or writes new data

into the cache. In the case of a write, the data

is

also written to the main memory.

b.

If

the tag

does

not match during a read cycle, a doubleword

is

read from main memory,

stored

in

the cache, and simultaneously presented to the 80386. The new tag

is

also

stored in the cache. During a write, if the tag does not match, the cache

is

not updated.

7.6.3

Example Cache Implementation

An implementation of a cache memory similar to the one described

in

this section

is

presented

in application note

AP-404, 80386 Cache Memory Example, order number 231978.

7-15

Loading...

Loading...