liD

INTERFACING

8.6.6.1

82258

AS

BUS

MASTER

The 82258 operating mode determines the type of bus interface it generates. In the 80286

mode, the 82258 generates the signals for direct interface with an 80286. In this example,

the 82258

is

set to 80286 mode because the 80386 resembles the 80286 more than the 80186

or 8086. The 82258

is

initialized to 80286 mode

by

holding its A23 pin high with a pullup

resistor during reset.

The 82258 interface must include logic for sharing control of the local bus with the

80386.

The

HOLD

and Hold Acknowledge

(HLDA)

pins

on

both the 80386 and the 82258 facili-

tate the transfer of bus control between the

80386 and the 82258.

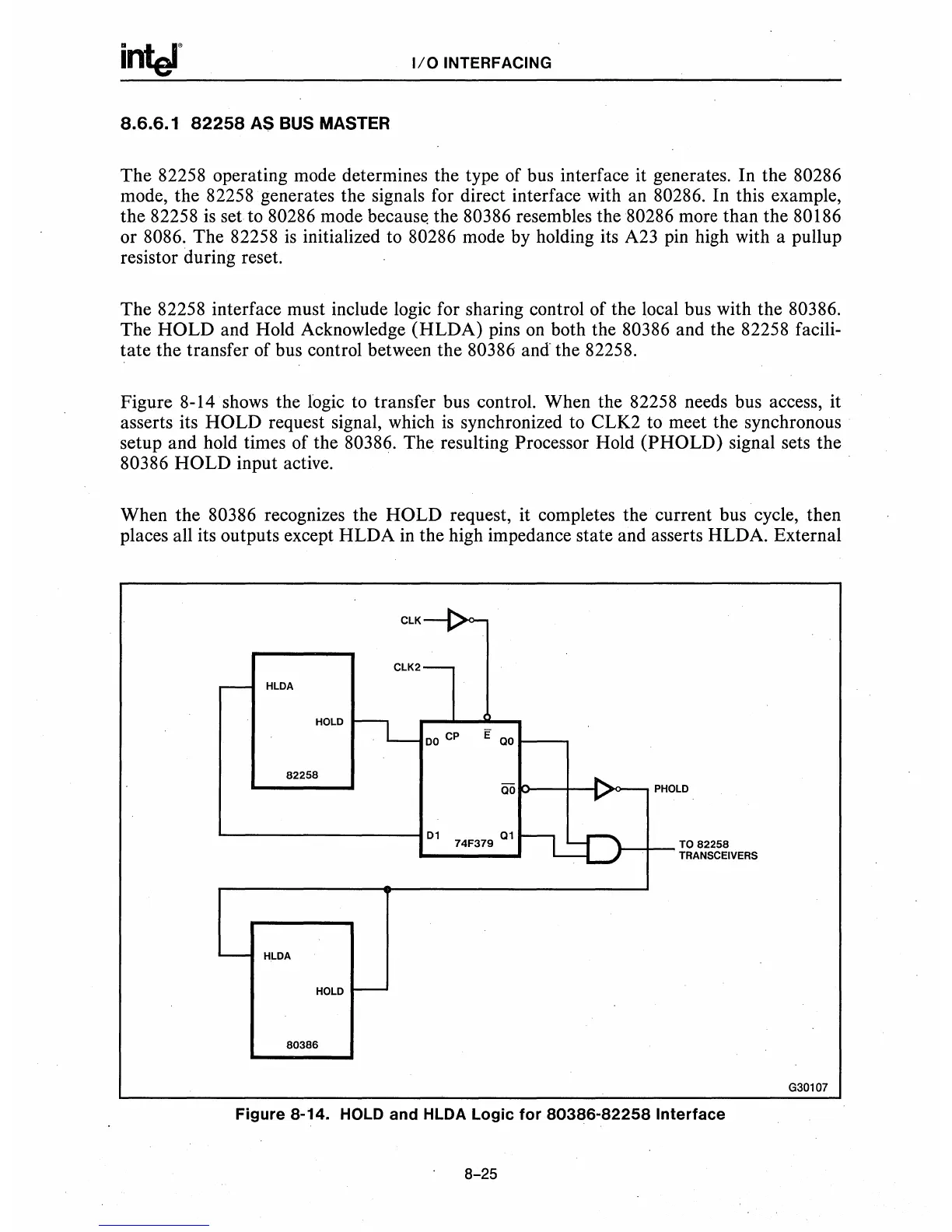

Figure 8-14 shows the

logic to transfer bus control. When the 82258 needs bus access,

it

asserts its

HOLD

request signal, which

is

synchronized to CLK2 to meet the synchronous

setup and hold times of the

80386. The resulting Processor Hold (PHOLD) signal sets the

80386

HOLD

input active.

When the

80386 recognizes the

HOLD

request, it completes the current bus cycle, then

places all its outputs except

HLDA

in the high impedance state and asserts HLDA. External

ClK

ClK2

HlDA

HOLD

82258

Qo

IO--+--L:>o----,

PHOlD

L.-

________

~

D1

74F379

Q1

HlDA

HOLD

80386

G30107

Figure

8-14. HOLD

and

HLDA

Logic

for

80386-82258

Interface

8-25

Loading...

Loading...