I/O

INTERFACING

logic must use HLDA to disable the output buffers of the 80386 bus controller, data bus,

and address bus, and enable the output buffers of the 82258 and its bus controller, data bus,

and address bus.

The wait-state generator must be started with the ALE output of the 82288 Bus Controller.

Although the 82258 can share wait-state generator logic with the 80386, the logic must be

modified to support longer wait states for 82258 cycles. The 82258 divides its CLK input by

two internally,

so

that its wait state requires two CLK cycles rather than one. In addition,

the READY # output must meet the 82258 input hold time requirement of

25

nanoseconds.

When the 82258 completes its operation, its HOLD request goes inactive (low), disabling

the 82258 output buffers and re-enabling the 80386 and its output buffer.

8.6.6.2

82258

AS

PERIPHERAL

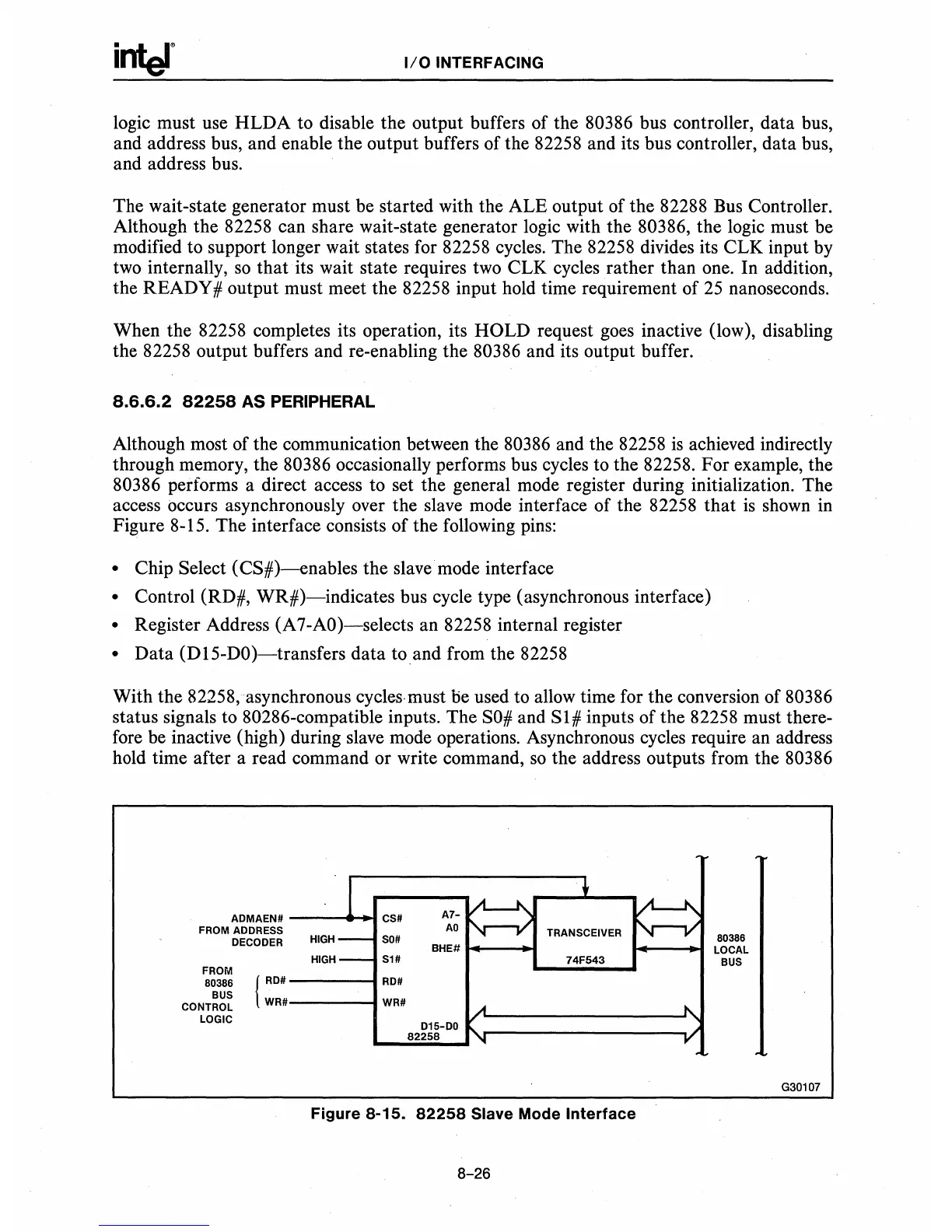

Although most of the communication between the 80386 and the 82258

is

achieved indirectly

through memory, the 80386 occasionally performs bus cycles to the 82258. For example, the

80386 performs a direct access to set the general mode register during initialization. The

access occurs asynchronously over the slave mode interface of the 82258

that

is

shown

in

Figure 8-15. The interface consists of the following pins:

• Chip Select

(CS#)-enables

the slave mode interface

• Control (RD#,

WR#)-indicates

bus cycle type (asynchronous interface)

• Register Address (A7-AO)-selects an 82258 internal register

• Data (D15-DO)-transfers data to and from the 82258

With the 82258,asynchronous cycles must be used to allow time for the conversion of 80386

status signals to 80286-compatible inputs. The

SO#

and S1# inputs of the 82258 must there-

fore be inactive (high) during slave mode operations. Asynchronous cycles require

an

address

hold time after a read command or write command,

so

the address outputs from the 80386

ADMAEN#

cs#

A7-

FROM ADDRESS

AO

DECODER

HIGH

50#

80386

BHE#

LOCAL

HIGH

51#

BUS

FROM

80386

{ RD#

RD#

BUS

WR#

WR#

CONTROL

LOGIC

D15-DO

82258

G30107

Figure

8-15.

82258

Slave Mode Interface

8-26

Loading...

Loading...